服務熱線

0755-83044319

發布時間:2022-03-10作者來源:薩科微瀏覽:3986

A:你們項目組芯片什么時間TO?

B:年底。

A: MPW?

B: 直接FULL MASK。

A:有錢。

B:芯片面積太大,占了6個SEAT,況且年底沒有合適時間點的shuttle。老大們就直接定了FULL MASK。

A:牛X!

TAPEOUT (TO):流片,指提交最終GDSII文件給Foundry工廠做加工。

MPW :多項目晶圓,將多個使用相同工藝的集成電路設計放在同一晶圓片上流片,制造完成后,每個設計可以得到數十片芯片樣品。

FULL MASK :“全掩膜”的意思,即制造流程中的全部掩膜都為某個設計服務。

Shuttle:就是MPW的時間,MPW的時間就是固定的,每個月或者每個季度有一次,有個很形象的翻譯:班車,到點就走。

SEAT:一個MPW的最小面積,就類似“班車”的座位,可以選擇一個或者幾個座位。

簡單來說,MPW就是和別的廠家共享一張掩模版,而FULL MASK則是獨享一張掩膜版。

如果芯片風險比較高,則可以先做MPW,測試沒有問題,再做FULL MASK。

主要的原因就是MASK(掩膜),比較貴,例如40nm的MASK大約在500萬左右,而28nm的MASK大約在1000萬左右,14nm的MASK大約在2500萬左右。不同廠家有差異,這里只是說明MASK的成本比較高。

如果芯片失敗,則MASK的錢就打水漂了。所以先做一次MPW也是分散風險的方法。

而MPW的問題就是,這個是按照面積來收錢的,例如在40nm的3mm*4mm 大約50萬人民幣等等。

這個叫做SEAT。一個SEAT就是3mm*4mm。

如果超過這個面積,就要額外收費。所以大芯片,是不合適做MPW的,如果是120mm2那需要10個SEAT,那么和整個MASK費用就一樣了。

這種情況做MPW就不合適了,所以從成本上來說是綜合考量的一件事情。

A:這次定了多少片WAFER?

B:24片?每片大約出1000片Die。考慮yield,大約有2萬片。

A:封裝怎么做?wirebonding還是flipchip。

B:Flip chip 。

A:是在foundry長好bump,還是封裝廠家來長bump。

B:foundry直接長好bump送到封測廠。

A: CP和FT都做,還是只做FT。

B:yield不高,基板也很貴,只做CP的話,會浪費太多基板。

A:對對對,這個年頭,基板太貴了。

B:我們老板搞到了1000萬片基板。

A:牛X!

Foundry:晶圓廠,專門從事芯片制造的廠家,例如臺積電(TSMC),中芯國際(SMIC),聯電(UMC)。對應的就是fabless,就是設計廠家,就是沒有晶圓廠。

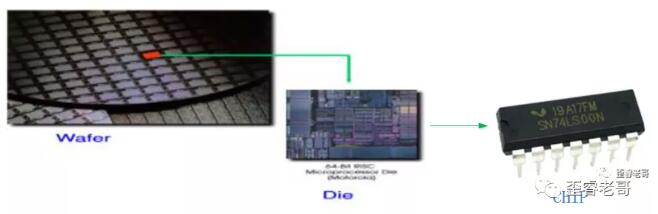

Wafer:晶圓。

Die:晶圓切割后,單個芯片的晶圓,這個需要加上封裝好的外殼才能能變成芯片。

Chip:最后封裝后的芯片。

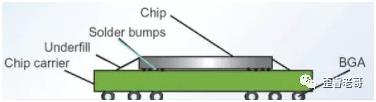

Bump:bumping指凸點。在wafer表面長出凸點(金,錫鉛,無鉛等等)后,(多用于倒裝工藝封裝上,也就是flipchip)。

Wirebonding:打線也叫Wire Bonding(壓焊,也稱為綁定,鍵合,絲焊)是指使用金屬絲(金線、鋁線等),利用熱壓或超聲能源,完成固態電路內部接線的連接,即芯片與電路或引線框架之間的連接。

Flipchip:Flip chip又稱倒裝片,是在I/Opad上沉積錫鉛球,然后將芯片翻轉加熱利用熔融的錫鉛球與陶瓷基板相結合。

CP:直接對晶圓進行測試,英文全稱Circuit Probing、Chip Probing,也稱為晶圓測試,測試對象是針對整片wafer中的每一個Die,目的是確保整片wafer中的每一個Die都能基本滿足器件的特征或者設計規格書,通常包括電壓、電流、時序和功能的驗證。可以用來檢測fab廠制造的工藝水平。

FT:FT測試,英文全稱FinalTest,是芯片出廠前的最后一道攔截。測試對象是針對封裝好的chip,CP測試之后會進行封裝,封裝之后進行FT測試。可以用來檢測封裝廠的工藝水平。

Yield:良率,芯片的良率這個和工藝比較相關,芯片有一定幾率失效,芯片越大,失效的幾率也越大。

解釋一下:為什么不直接做FT,而先做CP再做FT,這個是因為,CP針對晶圓,如果壞的Die就不用再去做封裝了,省下封裝的費用和基板的費用。

為什么不只做CP,而忽略FT,這個是因為CP測試完畢后,在封裝過程中還會引入芯片失效,所以還需要做FT來將失效的芯片去掉。

這個是一個權衡的過程,如果芯片良率足夠高,封裝成本不敏感,CP測試省掉,直接做FT也是可以的,因為CP測試本身也是需要成本。這個就是計算良率的問題。

目前來看,芯片行業整個供應鏈都很緊張,所以能夠搶到產能,包括搶wafer,搶基板,這些對于芯片廠商來說,都是當下的最重要的事情。

除了產能,其他都不是事!

A:這次SOC芯片選的哪個vendor的IP?

B:S的。

A:S的據說不錯,據說挺貴的,license要多少錢

B:200萬刀。

A:正常價。

B:收不收loyalty。

A: 收,每個芯片額外0.5刀。

B:牛X

IP:這個對應芯片來說,就是一個完整的功能模塊,

vendor:就是IP供應商,IP vendor,

license:允許使用這個IP,IP的授權

Loyalty:在用戶使用這個IP后,需要按照每個芯片收錢。

SOC:片上系統,就是把CPU,總線,外設,等等放到一個芯片內部實現。例如手機處理器就是一個復雜的SOC芯片。

IP這個是構成芯片最核心的組成單元,例如USB,PCIE,CPU等等都是IP,整個芯片都是IP集成的,芯片能夠做的比較復雜,核心就是IP的復用。例如那些做成幾千萬門,幾億門的,都是IP復用才能可以的。

如果有公司說全自主,沒有用過別人的IP,這種公司要么最牛X,例如大家都知道I家,要么就是極其簡單,ASIC。如果是做SOC大芯片這個領域,沒有用過別家的IP,這個不太可信。例如模擬的高速serdes,PCIe,ddr,mipi等等,全部自己搞,產品周期就會很漫長。蘋果的芯片也是先用了別人的IP,公司達到萬億美金產值,搞那么多人來自己搞替換。

初創公司,不用外部IP,從0開始搞,這個不是思路,是絕路。

一般是核心IP自己搞(也沒有賣的),外圍成熟IP有成熟就賣成熟IP,減少上市的時間,盡快迭代占了市場,逐漸核心替換,才是正常公司的思維。

千萬不要被“全自研”給唬住了。

一般IP的license的費用和IP的loyalty的費用可以談,如果量很大的話,license的費用就會比較低,loyalty的費用單片不高,但是如果量很大,最后就很可觀,也有IP廠商不收license費用,最后只收loyalty的費用,這樣IP廠商和芯片廠商的利益就綁在一起了。

A: 你們項目的RTL freeze了嗎?

B:freeze了,verification都差不多了。Power simlulation正在搞。

A:年底的shuttle應該沒有問題吧

B:可能要delay,netlist還沒有freeze

A:啥原因?

B:SDC還有點問題,后端反饋,timing沒有clean;

A:那你們要抓緊了,需要去做merge,需要提前2周出gds。

B:是的,我們芯片分了10個模塊單獨harden,難度還是很大的。

A:牛X

RTL:register-transferlevel(RTL)是用于描述同步數字電路的硬件描述語言。

Netlist:網表,RTL需要通過綜合以后才能變成網表。

SDC:設計提供約束文件,綜合工具需要這個約束文件才能講RTL轉換成netlist。

SDC主要描述內容包括:芯片工作頻率,芯片IO時序,設計規則,特殊路徑,不用check的路徑等等。

Freeze:指設計凍結,不能再改動的了,例如RTL freeze ,就是代碼凍結了,netlist freeze 就是網表凍結了,不能再改了。

Verification:芯片功能驗證,目前主要指芯片驗證方法論(UVM),主要通過驗證兩者RTL和reference model是不是一致,簡稱A=B,見我原來寫的《降低芯片流片失敗風險的"七種[敏感詞]"》,里面有關于驗證的描述。

Simulation:仿真, 仿真通常是生成波形,一般來說,芯片的功能,verification ,芯片的功耗,可以simulation,比較直觀反應真實的場景。

Hardren:指某個IP以硬模塊的形式來實現。

GDS:netlist經過后端工具編程版圖,而版圖提交給流片廠家(foundry)的就是GDS II

Merge:就是講單獨hardren的模塊,拼接進去。

merge這個是IP廠商保護IP的一種手段,一般放在foundry的專門的merge room中,才能進行。這樣芯片廠商最終需要去foundry廠商那里拼接完成,得到最終的GDSII。

delay: 延期,這個次是芯片工程師最不愿意的詞了,也是最經常碰到的詞,一個環節不慎,就要delay,這個意味著問題出現,成本增加,周期加長。

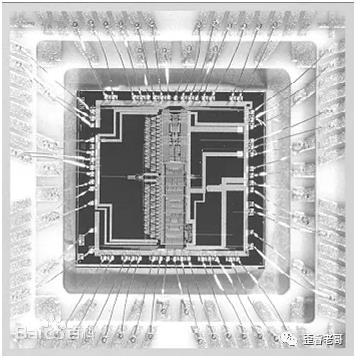

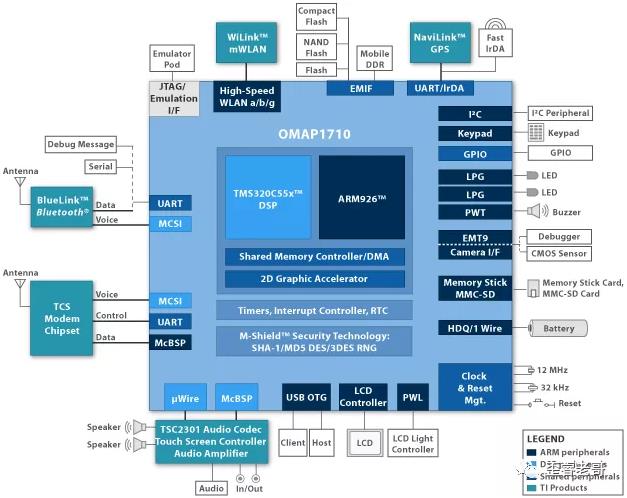

如果芯片太大,可以把其中一部分來hardren,頂層就是幾個harden模塊像拼拼圖一樣拼起來,大型多核CPU一般都是這樣做的,在版圖上很容易看出來。

從上圖來看,這些四四方方的位置,都是單獨harden后,在芯片頂層拼起來的。

單獨harden的好處是,可以多個芯片后端設計團隊并行設計,大家同時設計,設計完畢,拼接一下就行。

如果有問題的話,直接改某個模塊,而不用整個芯片都返工。當然,改完某個模塊后,面積還要保持一致,否則就拼不進去了,改完了后,整個頂層也要重新跑一遍流程。

這個就是大芯片難度大的原因,也容易delay(延期);

大芯片的設計難度明顯比小芯片設計難度大,周期也長。

大芯片類似大電影,需要大咖,大制作,燈光,道具,劇本,人員,后期,等等;小芯片類似小視頻,都是芯片,其中的復雜程度,協同程度,需要人力,物力,財力都是完全不同的。

現在有個問題:大芯片賺錢,還是小芯片賺錢?

這個也不一定,你見過幾億拍的大片,沒幾個人看,虧得一塌糊涂,而一個人拍的小視頻也可以火遍全網。

但是,大芯片是能力,國之重器,非常重要。

上面是比較常用的一些“黑話”。

當然芯片工程師的“黑話”,遠不止于此。

就像斯皮爾伯格導演《貓鼠游戲》里的萊昂納多一樣,他偽裝成記者和一個資深飛行員套話,記住了這些黑話,就能偽裝成一個飛行員,從而成功的登上飛機。

而知道上面這些芯片工程師的“黑話”,還遠不能混為一個芯片工程師。

由于芯片分工太細,很多芯片工程師對于這些不同工序的黑話,也不能全部知道。

這個就類似我們討論芯片的時候,芯片流程太復雜,以至于很難看清全貌。

世界已經變了。

分工越來越細,只能管中窺豹。

世界如此,芯片也如此。

免責聲明:本文轉載自“芯師爺”,本文僅代表作者個人觀點,不代表薩科微及行業觀點,只為轉載與分享,支持保護知識產權,轉載請注明原出處及作者,如有侵權請聯系我們刪除。

公司電話:+86-0755-83044319

傳真/FAX:+86-0755-83975897

郵箱:1615456225@qq.com

QQ:3518641314 李經理

QQ:202974035 陳經理

地址:深圳市龍華新區民治大道1079號展滔科技大廈C座809室

友情鏈接:站點地圖 薩科微官方微博 立創商城-薩科微專賣 金航標官網 金航標英文站

Copyright ?2015-2022 深圳薩科微半導體有限公司 版權所有 粵ICP備20017602號-1