一項技術能從相對狹窄的專業領域變得廣為人知,有歷史的原因,也離不開[敏感詞]公司的推波助瀾,把SiP帶給大眾的是蘋果(Apple),而先進封裝能引起公眾廣泛關注則是因為臺積電(TSMC)。 蘋果說,我的i Watch采用了SiP技術,SiP從此廣為人知;臺積電說,除了先進工藝,我還要搞先進封裝,先進封裝因此被業界提到了和先進工藝同等重要的地位。 近些年,先進封裝技術不斷涌現,新名詞也層出不窮,讓人有些眼花繚亂,目前可以列出的先進封裝相關的名稱至少有幾十種。 例如:WLP(Wafer Level Package), FIWLP(Fan-in Wafer Level Package), FOWLP(Fan-Out Wafer Level Package), eWLB(embedded Wafer Level BallGrid Array), CSP(Chip Scale Package), WLCSP(Wafer Level Chip Scale Package), CoW(Chip on Wafer), WoW(Wafer on Wafer), FOPLP(Fan-Out Panel Level Package), InFO(Integrated Fan-Out), CoWoS(Chip-on-Wafer-on-Substrate), HBM(High-Bandwidth Memory), HMC(Hybrid MemoryCube), Wide-IO(Wide Input Output), EMIB(Embedded Multi-Die Interconect Bridge), Foveros, Co-EMIB, ODI(Omni-Directional Interconnect), 3D IC, SoIC, X-Cube…等等…這些都屬于先進封裝技術。 如何區分并理解這些讓人眼花繚亂的先進封裝技術呢?這就是本文要告訴讀者的。 首先,為了便于區分,我們將先進封裝分為兩大類:

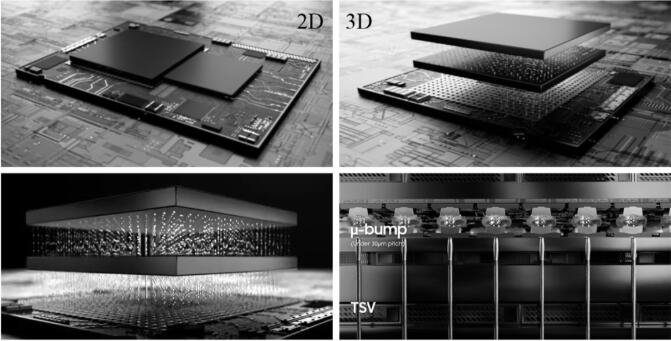

① 基于XY平面延伸的先進封裝技術,主要通過RDL進行信號的延伸和互連;

② 基于Z軸延伸的先進封裝技術,主要是通過TSV進行信號延伸和互連。

基于XY平面延伸的 先進封裝技術

這里的XY平面指的是Wafer或者芯片的XY平面,這類封裝的鮮明特點就是沒有TSV硅通孔,其信號延伸的手段或技術主要通過RDL層來實現,通常沒有基板,其RDL布線時是依附在芯片的硅體上,或者在附加的Molding上。因為最終的封裝產品沒有基板,所以此類封裝都比較薄,目前在智能手機中得到廣泛的應用。

1.FOWLP

FOWLP (Fan-out Wafer Level Package)是WLP(Wafer Level Package)的一種,因此我們需要先了解WLP晶圓級封裝。

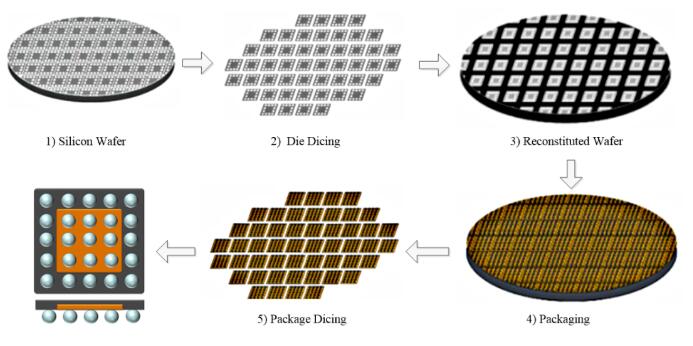

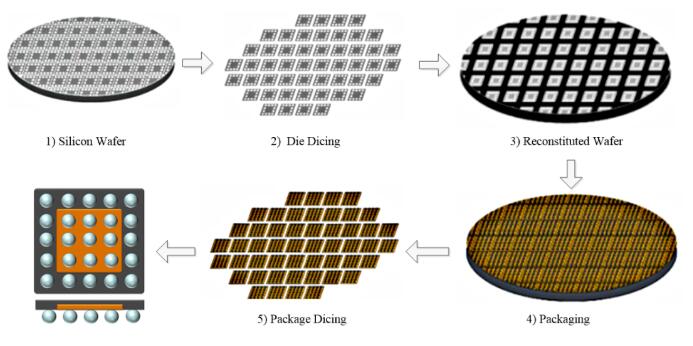

在WLP技術出現之前,傳統封裝工藝步驟主要在裸片切割分片后進行,先對晶圓(Wafer)進行切割分片(Dicing),然后再封裝(Packaging)成各種形式。

WLP于2000年左右問世,有兩種類型:Fan-in(扇入式)和Fan-Out(扇出式)WLP晶圓級封裝和傳統封裝不同,在封裝過程中大部分工藝過程都是對晶圓進行操作,即在晶圓上進行整體封裝(Packaging),封裝完成后再進行切割分片。 因為封裝完成后再進行切割分片,因此,封裝后的芯片尺寸和裸芯片幾乎一致,因此也被稱為CSP(Chip Scale Package)或者WLCSP(Wafer Level Chip Scale Packaging),此類封裝符合消費類電子產品輕、小、短、薄化的市場趨勢,寄生電容、電感都比較小,并具有低成本、散熱佳等優點。

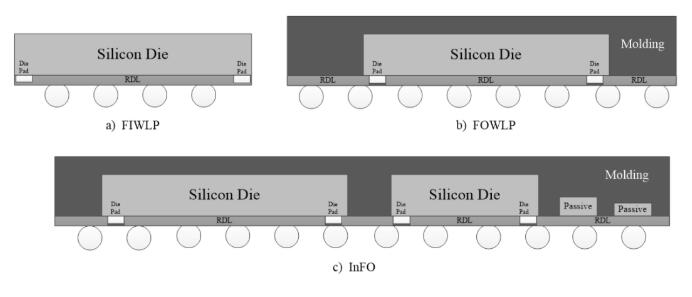

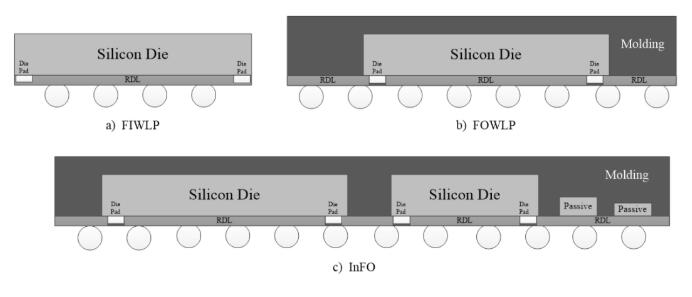

開始WLP多采用Fan-in型態,可稱之為Fan-in WLP 或者FIWLP,主要應用于面積較小、引腳數量少的芯片。

隨著IC工藝的提升,芯片面積縮小,芯片面積內無法容納足夠的引腳數量,因此衍生出Fan-Out WLP 封裝形態,也稱為FOWLP,實現在芯片面積范圍外充分利用RDL做連接,以獲取更多的引腳數。

FOWLP,由于要將RDL和Bump引出到裸芯片的外圍,因此需要先進行裸芯片晶圓的劃片分割,然后將獨立的裸芯片重新配置到晶圓工藝中,并以此為基礎,通過批量處理、金屬化布線互連,形成最終封裝。FOWLP封裝流程如下圖所示。

FOWLP受到很多公司的支持,不同的公司也有不同的命名方法,下圖所示為各大公司的提供的FOWLP。

無論是采用Fan-in還是Fan-out,WLP晶圓級封裝和PCB的連接都是采用倒裝芯片形式,芯片有源面朝下對著印刷電路板,可以實現最短的電路徑,這也保證了更高的速度和更少的寄生效應。另一方面,由于采用批量封裝,整個晶圓能夠實現一次全部封裝,成本的降低也是晶圓級封裝的另一個推動力量。

2.INFO InFO(Integrated Fan-out)是臺積電(TSMC)于2017年開發出來的FOWLP先進封裝技術,是在FOWLP工藝上的集成,可以理解為多個芯片Fan-Out工藝的集成,而FOWLP則偏重于Fan-Out封裝工藝本身。 InFO給予了多個芯片集成的空間,可應用于射頻和無線芯片的封裝,處理器和基帶芯片封裝,圖形處理器和網絡芯片的封裝。下圖為FIWLP,FOWLP和InFO對比示意圖。

蘋果iPhone處理器早年一直是三星來生產,但臺積電卻從蘋果A11 開始,接連獨拿兩代iPhone處理器訂單,關鍵之一,就在于臺積電全新封裝技術InFO,能讓芯片與芯片之間直接互連,減少厚度,騰出寶貴的空間給電池或其他零件使用。

蘋果從 iPhone 7 就開始InFO封裝,后續繼續在用,iPhone 8、iPhone X,包括以后其他品牌的手機也會開始普遍使用這個技術。蘋果和臺積電的加入改變了FOWLP技術的應用狀況,將使市場開始逐漸接受并普遍應用FOWLP(InFO)封裝技術。

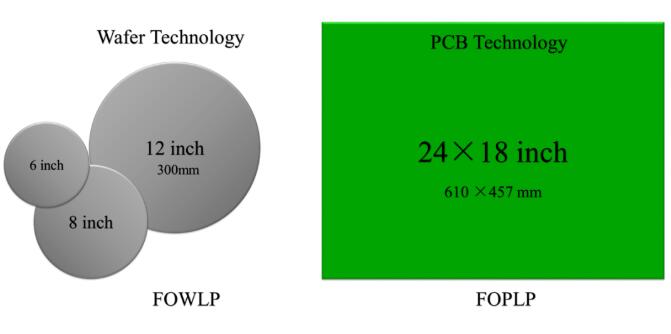

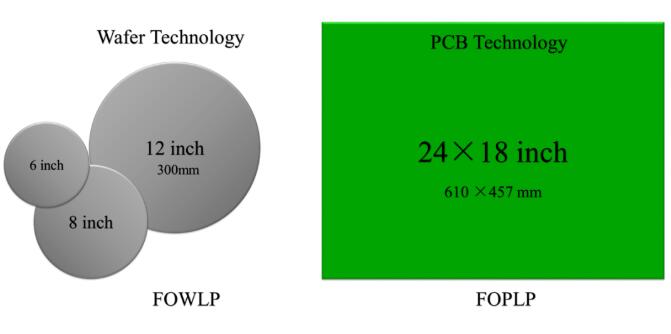

3.FOPLP FOPLP(Fan-out Panel Level Package)面板級封裝,借鑒了FOWLP的思路和技術,但采用了更大的面板,因此可以量產出數倍于 300 毫米硅晶圓芯片的封裝產品。 FOPLP技術是FOWLP 技術的延伸,在更大面積的方形載板上進行Fan-Out制程,因此被稱為 FOPLP 封裝技術,其Panel載板可以采用PCB載板,或者液晶面板用的玻璃載板。 目前而言,FOPLP采用了如 24×18英寸(610×457mm)的PCB載板,其面積大約是 300 mm硅晶圓的4 倍,因而可以簡單的視為在一次的制程下,就可以量產出 4 倍于300 mm硅晶圓的先進封裝產品。 和FOWLP工藝相同,FOPLP 技術可以將封裝前后段制程整合進行,可以將其視為一次的封裝制程,因此可大幅降低生產與材料等各項成本。下圖為FOWLP和FOPLP比較。

FOPLP采用了PCB上的生產技術進行RDL的生產,其線寬、線間距目前均大于10um,采用SMT設備進行芯片和無源器件的貼裝,由于其面板面積遠大于晶圓面積,因而可以一次封裝更多的產品。相對FOWLP,FOPLP具有更大的成本優勢。目前,全球各大封裝業者包括三星電子、日月光均積極投入到FOPLP 制程技術中。

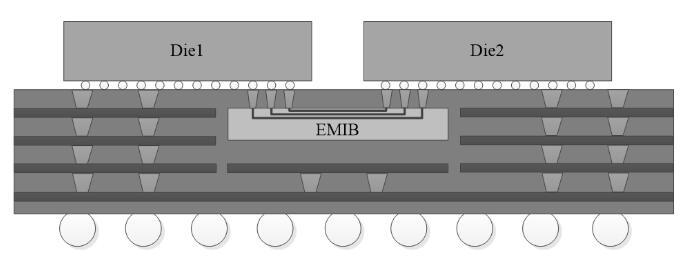

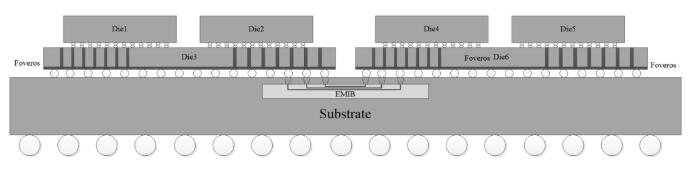

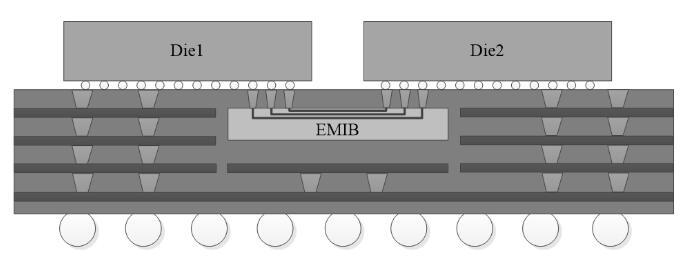

4.EMIB EMIB(Embedded Multi-Die Interconnect Bridge)嵌入式多芯片互連橋先進封裝技術是由英特爾提出并積極應用的,和前面描述的3種先進封裝不同,EMIB是屬于有基板類封裝,因為EMIB也沒有TSV,因此也被劃分到基于XY平面延伸的先進封裝技術。 EMIB理念跟基于硅中介層的2.5D封裝類似,是通過硅片進行局部高密度互連。與傳統2.5封裝的相比,因為沒有TSV,因此EMIB技術具有正常的封裝良率、無需額外工藝和設計簡單等優點。 傳統的SoC芯片,CPU、GPU、內存控制器及IO控制器都只能使用一種工藝制造。采用EMIB技術,CPU、GPU對工藝要求高,可以使用10nm工藝, IO單元、通訊單元可以使用14nm工藝,內存部分則可以使用22nm工藝,采用EMIB先進封裝技術可以把三種不同工藝整合到一起成為一個處理器。下圖是EMIB示意圖。

和硅中介層(interposer)相比,EMIB硅片面積更微小、更靈活、更經濟。EMIB封裝技術可以根據需要將CPU、IO、GPU甚至FPGA、AI等芯片封裝到一起,能夠把10nm、14nm、22nm等多種不同工藝的芯片封裝在一起做成單一芯片,適應靈活的業務的需求。

通過EMIB方式,KBL-G平臺將英特爾酷睿處理器與AMD Radeon RX Vega M GPU整合在一起,同時具備了英特爾處理器強大的計算能力與AMD GPU出色的圖形能力,并且還有著[敏感詞]的散熱體驗。這顆芯片創造了歷史,也讓產品體驗達到了一個新的層次。

基于Z軸延伸的 先進封裝技術

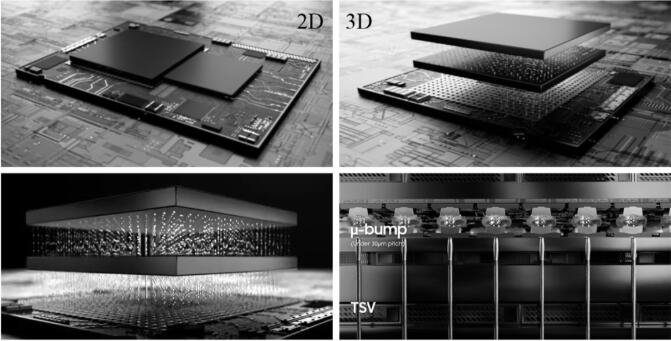

基于Z軸延伸的先進封裝技術主要是通過TSV進行信號延伸和互連,TSV可分為2.5D TSV和3D TSV,通過TSV技術,可以將多個芯片進行垂直堆疊并互連。

在3D TSV技術中,芯片相互靠得很近,所以延遲會更少,此外互連長度的縮短,能減少相關寄生效應,使器件以更高的頻率運行,從而轉化為性能改進,并更大程度的降低成本。 TSV技術是三維封裝的關鍵技術,包括半導體集成制造商、集成電路制造代工廠、封裝代工廠、新興技術開發商、大學與研究所以及技術聯盟等研究機構都對 TSV 的工藝進行了多方面的研發。 此外,需要讀者注意,雖然基于Z軸延伸的先進封裝技術主要是通過TSV進行信號延伸和互連,但RDL同樣是不可或缺的,例如,如果上下層芯片的TSV無法對齊時,就需要通過RDL進行局部互連。

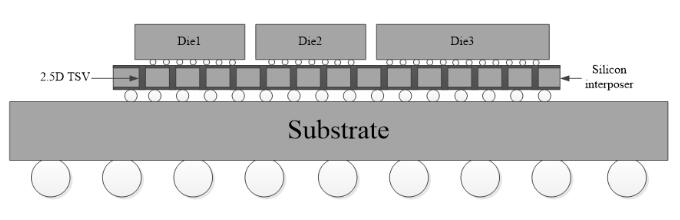

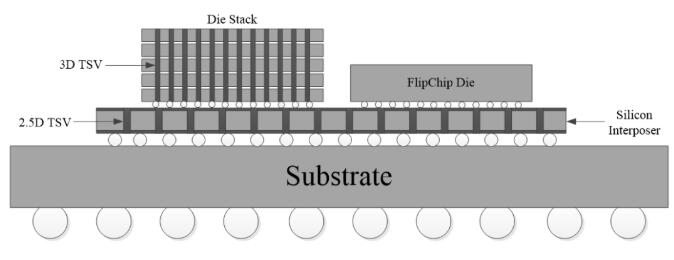

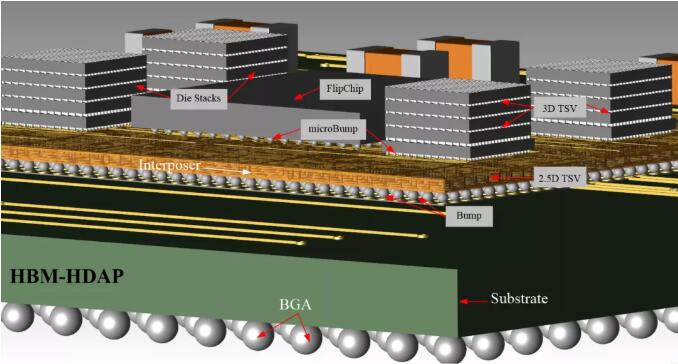

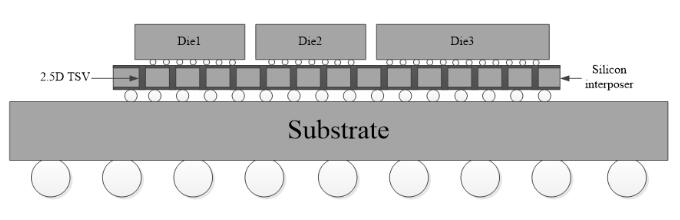

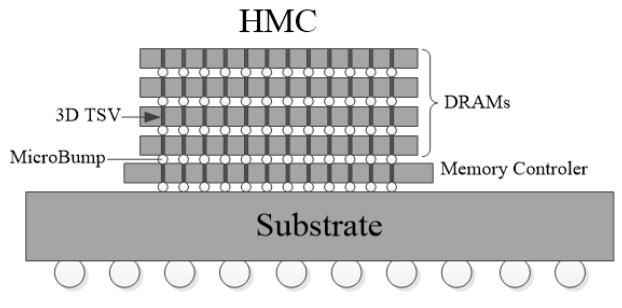

5.CoWoS CoWoS(Chip-on-Wafer-on-Substrate)是臺積電推出的 2.5D封裝技術,CoWoS是把芯片封裝到硅轉接板(中介層)上,并使用硅轉接板上的高密度布線進行互連,然后再安裝在封裝基板上,如下圖所示。

CoWoS和前面講到的InFO都來自臺積電,CoWoS有硅轉接板Silicon Interposer,InFO則沒有。CoWoS針對高端市場,連線數量和封裝尺寸都比較大。InFO針對性價比市場,封裝尺寸較小,連線數量也比較少。

臺積電2012年就開始量產CoWoS,通過該技術把多顆芯片封裝到一起,通過Silicon Interposer高密度互連,達到了封裝體積小,性能高、功耗低,引腳少的效果。

CoWoS技術應用很廣泛,英偉達的GP100、戰勝柯潔的AlphaGo背后的Google芯片TPU2.0都是采用CoWoS技術,人工智能AI的背后也是有CoWoS的貢獻。目前,CoWoS已經獲得NVIDIA、AMD、Google、XilinX、華為海思等高端芯片廠商的支持。

6.HBM HBM(High-Bandwidth Memory )高帶寬內存,主要針對高端顯卡市場。HBM使用了3D TSV和2.5D TSV技術,通過3D TSV把多塊內存芯片堆疊在一起,并使用2.5D TSV技術把堆疊內存芯片和GPU在載板上實現互連。下圖所示為HBM技術示意圖。

HBM目前有三個版本,分別是HBM、HBM2和HBM2E,其帶寬分別為128 GBps/Stack、256 GBps/Stack和307 GBps/Stack,[敏感詞]的HBM3還在研發中。 AMD、NVIDIA和海力士主推的HBM標準,AMD首先在其旗艦顯卡首先使用HBM標準,顯存帶寬可達512 GBps,NVIDIA也緊追其后,使用HBM標準實現1TBps的顯存帶寬。和DDR5相比,HBM性能提升超過了3倍,但功耗卻降低了50%。

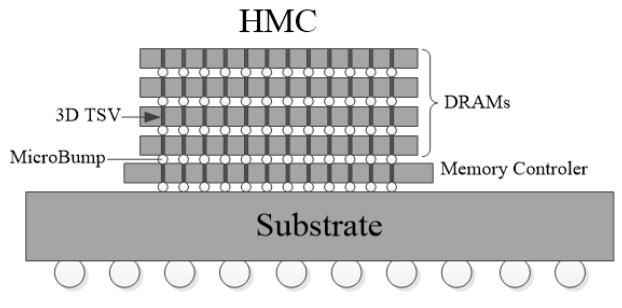

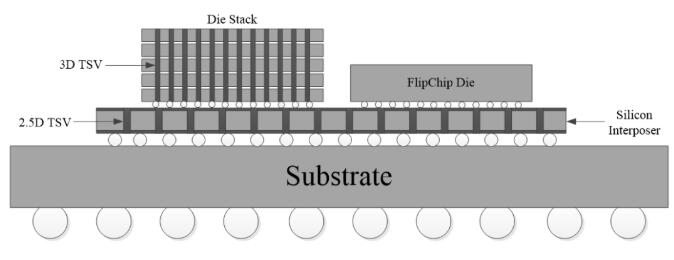

7.HMC HMC(Hybrid Memory Cube)混合存儲立方體,其標準由美光主推,目標市場是高端服務器市場,尤其是針對多處理器架構。HMC使用堆疊的DRAM芯片實現更大的內存帶寬。另外HMC通過3D TSV集成技術把內存控制器(Memory Controller)集成到DRAM堆疊封裝里。下圖所示為HMC技術示意圖。

對比HBM和HMC可以看出,兩者很相似,都是將DRAM芯片堆疊并通過3D TSV互連,并且其下方都有邏輯控制芯片,兩者的不同在于:HBM通過Interposer和GPU互連,而HMC則是直接安裝在Substrate上,中間缺少了Interposer和2.5D TSV。 在HMC堆疊中,3D TSV的直徑約為5~6um,數量超過了2000+,DRAM芯片通常減薄到50um,之間通過20um的MicroBump將芯片相連。 以往內存控制器都做在處理器里,所以在高端服務器里,當需要使用大量內存模塊時,內存控制器的設計非常復雜。現在把內存控制器集成到內存模塊內,則內存控制器的設計就大大地簡化了。此外,HMC使用高速串行接口(SerDes)來實現高速接口,適合處理器和內存距離較遠的情況。

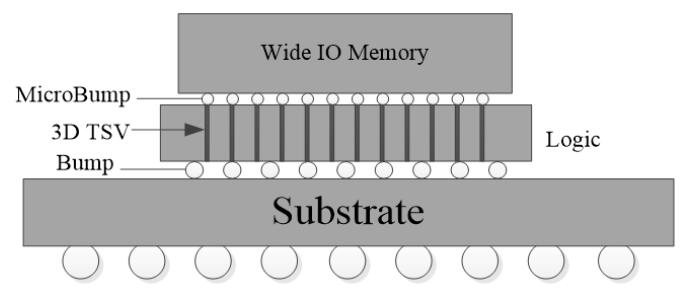

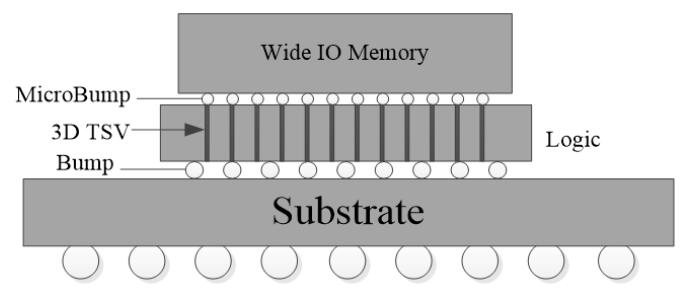

8.Wide-IO Wide-IO(Wide Input Output)寬帶輸入輸出技術由三星主推,目前已經到了第二代,可以實現最多512bit的內存接口位寬,內存接口操作頻率[敏感詞]可達1GHz,總的內存帶寬可達68GBps,是DDR4接口帶寬(34GBps)的兩倍。 Wide-IO通過將Memory芯片堆疊在Logic芯片上來實現,Memory芯片通過3D TSV和Logic芯片及基板相連接,如下圖所示。

Wide-IO具備TSV架構的垂直堆疊封裝優勢,有助打造兼具速度、容量與功率特性的移動存儲器,滿足智慧型手機、平板電腦、掌上型游戲機等行動裝置的需求,其主要目標市場是要求低功耗的移動設備。

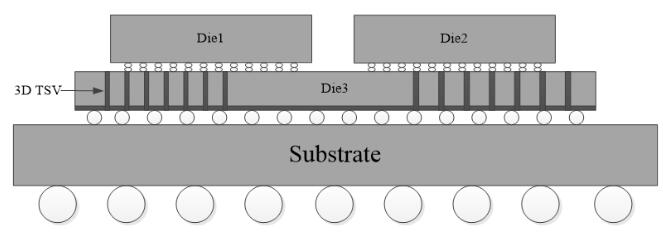

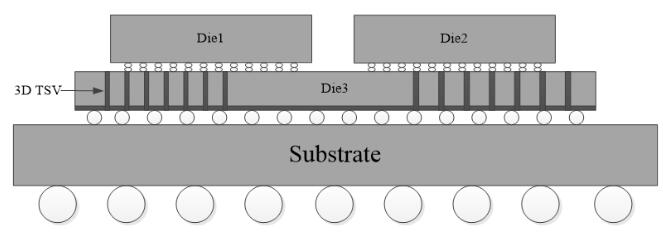

9.Foveros 除了前面介紹過的EMIB先進封裝之外,Intel還推出了Foveros有源板載技術。在Intel的技術介紹中,Foveros被稱作3D Face to Face Chip Stack for heterogeneous integration,三維面對面異構集成芯片堆疊。 EMIB與Foveros的區別在于前者是2D封裝技術,而后者則是3D堆疊封裝技術,與2D的EMIB封裝方式相比,Foveros更適用于小尺寸產品或對內存帶寬要求更高的產品。其實EMIB和Foveros在芯片性能、功能方面的差異不大,都是將不同規格、不同功能的芯片集成在一起來發揮不同的作用。不過在體積、功耗等方面,Foveros 3D堆疊的優勢就顯現了出來。Foveros每比特傳輸的數據的功率非常低,Foveros技術要處理的是Bump間距減小、密度增大以及芯片堆疊技術。 下圖所示是 Foveros 3D封裝技術示意圖。

[敏感詞]Foveros 3D堆疊設計的主板芯片LakeField,它集成了10nm Ice Lake處理器以及22nm核心,具備完整的PC功能,但體積只有幾枚美分硬幣大小。 雖說Foveros是更為先進的3D封裝技術,但它與EMIB之間并非取代關系,英特爾在后續的制造中會將二者結合起來使用。

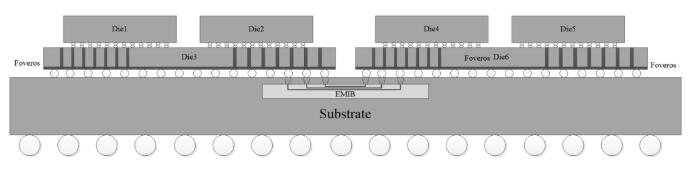

10.Co-EMIB(Foveros + EMIB) Co-EMIB是EMIB和Foveros的綜合體,EMIB主要是負責橫向的連結,讓不同內核的芯片像拼圖一樣拼接起來,而Foveros則是縱向堆棧,就好像蓋高樓一樣,每層樓都可以有完全不同的設計,比如說一層為健身房,二層當寫字樓,三層作公寓。 將EMIB和Foveros合并起來的封裝技術被稱作Co-EMIB,是可以具有彈性更高的芯片制造方法,可以讓芯片在堆疊的同時繼續橫向拼接。因此,該技術可以將多個3D Foveros芯片通過EMIB拼接在一起,以制造更大的芯片系統。下圖是Co-EMIB技術示意圖。

Co-EMIB封裝技術能提供堪比單片的性能,達成這個技術的關鍵,就是ODI(Omni-Directional Interconnect)全向互連技術。ODI具有兩種不同型態,除了打通不同層的電梯型態連接外,也有連通不同立體結構的天橋,以及層之間的夾層,讓不同的芯片組合可以有極高的彈性。ODI封裝技術可以讓芯片既實現水平互連,又可以實現垂直互連。

Co-EMIB通過全新的3D + 2D封裝方式,將芯片設計思維也從過去的平面拼圖,變成堆積木。因此,除了量子計算等革命性的全新計算架構外,CO-EMIB可以說是在維持并延續現有計算架構與生態的[敏感詞]作法。

11.SoIC

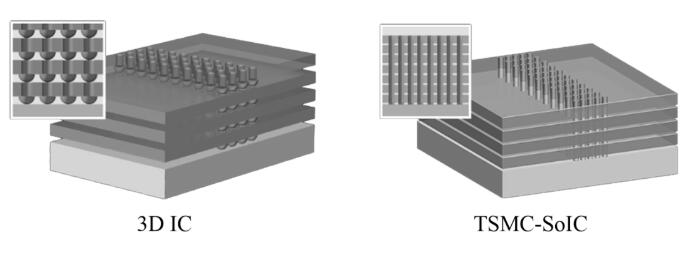

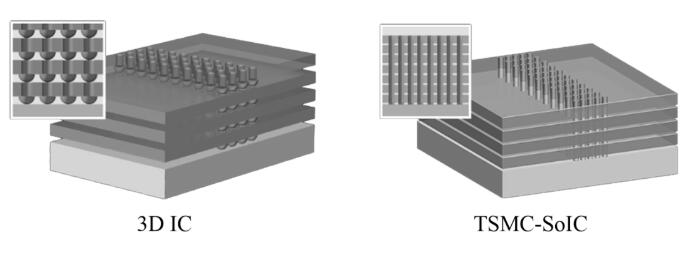

SoIC也稱為TSMC-SoIC,是臺積電提出的一項新技術——集成片上系統(System-on-Integrated-Chips),預計在2021年,臺積電的SoIC技術就將進行量產。 究竟什么是SoIC?所謂SoIC是一種創新的多芯片堆棧技術,能對10納米以下的制程進行晶圓級的集成。該技術最鮮明的特點是沒有凸點(no-Bump)的鍵合結構,因此具有有更高的集成密度和更佳的運行性能。 SoIC包含CoW(Chip-on-wafer)和WoW(Wafer-on-wafer)兩種技術形態,從TSMC的描述來看,SoIC就一種WoW晶圓對晶圓或CoW芯片對晶圓的直接鍵合(Bonding)技術,屬于Front-End 3D技術(FE 3D),而前面提到的InFO和CoWoS則屬于Back-End 3D技術(BE 3D)。TSMC和Siemens EDA(Mentor)就SoIC技術進行合作,推出了相關的設計與驗證工具。 下圖是3D IC和SoIC集成的比較。

具體的說,SoIC和3D IC的制程有些類似,SoIC的關鍵就在于實現沒有凸點的接合結構,并且其TSV的密度也比傳統的3D IC密度更高,直接通過極微小的TSV來實現多層芯片之間的互聯。如上圖所示是3D IC和SoIC兩者中TSV密度和Bump尺寸的比較。可以看出,SoIC的TSV密度要遠遠高于3D IC,同時其芯片間的互聯也采用no-Bump的直接鍵合技術,芯片間距更小,集成密度更高,因而其產品也比傳統的3D IC有更高的功能密度。

12.X-Cube X-Cube(eXtended-Cube)是三星宣布推出的一項3D集成技術,可以在較小的空間中容納更多的內存,并縮短單元之間的信號距離。 X-Cube用于需要高性能和帶寬的工藝,例如5G,人工智能以及可穿戴或移動設備以及需要高計算能力的應用中。X-Cube利用TSV技術將SRAM堆疊在邏輯單元頂部,可以在更小的空間中容納更多的存儲器。 從X-Cube技術展示圖可以看到,不同于以往多個芯片2D平行封裝,X-Cube?3D封裝允許多枚芯片堆疊封裝,使得成品芯片結構更加緊湊。芯片之間采用了TSV技術連接,降低功耗的同時提高了傳輸的速率。該技術將會應用于最前沿的5G、AI、AR、HPC、移動芯片以及VR等領域。

X-Cube技術大幅縮短了芯片間的信號傳輸距離,提高數據傳輸速度,降低功耗,并且還可以按客戶需求定制內存帶寬及密度。目前X-Cube技術已經可以支持7nm及5nm工藝,三星將繼續與全球半導體公司合作,將該技術部署在新一代高性能芯片中。

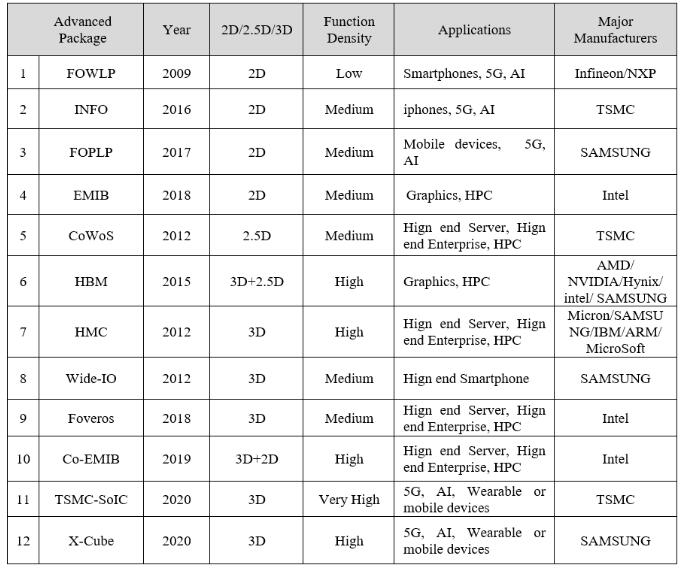

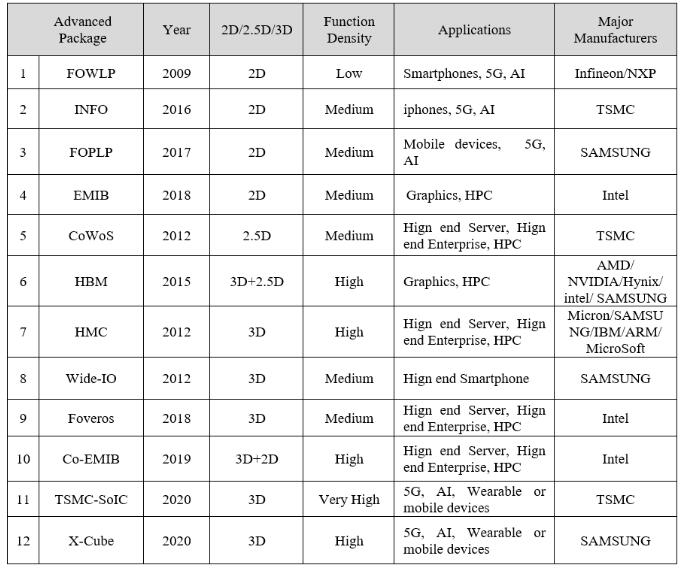

總結 先進封裝技術 本文中,我們講述了12種當今最主流的先進封裝技術。下表是對這些主流先進封裝技術橫向比較。

從對比中我們可以看出,先進封裝的出現和快速發展主要是在近10年間,其集成技術主要包括2D、2.5D、3D、3D+2D、3D+2.5D幾種類型,功能密度也有低、中、高、極高幾種,應用領域包括了5G,AI,可穿戴設備,移動設備、高性能服務器、高性能計算、高性能顯卡等領域,主要應用廠商包括TSMC、Intel、SAMSUNG等[敏感詞]芯片廠商,這也反映出先進封裝和芯片制造融合的趨勢。

最后,我們總結一下:先進封裝的目的就是:

提升功能密度,縮短互連長度,提升系統性能,降低整體功耗。

先進封裝對EDA工具也提出了新的要求,EDA工具需要既能支持FIWLP、FOWLP、2.5DTSV和3D TSV設計,也需要能支持多基板設計,因為一款產品中硅中介層(inteposer)和封裝基板(Substrate)經常集成在一起,各大EDA公司紛紛推出了新的工具來支持先進封裝的設計和驗證,包括Synopsys, Cadence, Siemens EDA(Mentor)都積極參與其中。

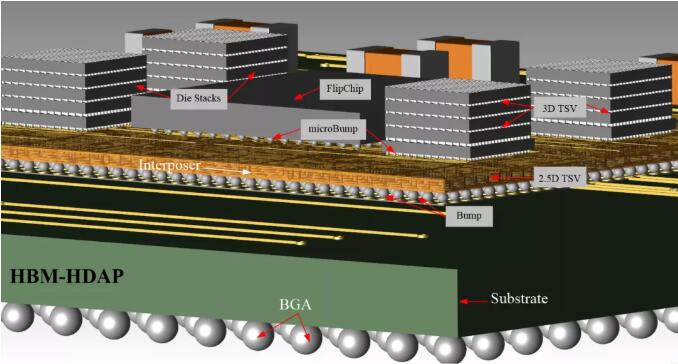

下圖所示為Siemens EDA XPD工具先進封裝設計截圖,該設計包含了3D TSV和2.5D TSV設計,Interposer,Substrate,FlipChip,Microbump,BGA等元素,在EDA工具中得到了詳盡和精準的體現。關于先進封裝的詳細設計方法可參考近期即將出版的新書《基于SiP技術的微系統》。

典型的先進封裝設計(Siemens EDA XPD設計截圖)

免責聲明:本文轉載自“SiP與先進封裝技術”,支持保護知識產權,轉載請注明原出處及作者,如有侵權請聯系我們刪除。

公司電話:+86-0755-83044319

傳真/FAX:+86-0755-83975897

郵箱:1615456225@qq.com

QQ:3518641314 李經理

QQ:332496225 丘經理

地址:深圳市龍華新區民治大道1079號展滔科技大廈C座809室

無論是采用Fan-in還是Fan-out,WLP晶圓級封裝和PCB的連接都是采用倒裝芯片形式,芯片有源面朝下對著印刷電路板,可以實現最短的電路徑,這也保證了更高的速度和更少的寄生效應。另一方面,由于采用批量封裝,整個晶圓能夠實現一次全部封裝,成本的降低也是晶圓級封裝的另一個推動力量。

2.INFO InFO(Integrated Fan-out)是臺積電(TSMC)于2017年開發出來的FOWLP先進封裝技術,是在FOWLP工藝上的集成,可以理解為多個芯片Fan-Out工藝的集成,而FOWLP則偏重于Fan-Out封裝工藝本身。 InFO給予了多個芯片集成的空間,可應用于射頻和無線芯片的封裝,處理器和基帶芯片封裝,圖形處理器和網絡芯片的封裝。下圖為FIWLP,FOWLP和InFO對比示意圖。

無論是采用Fan-in還是Fan-out,WLP晶圓級封裝和PCB的連接都是采用倒裝芯片形式,芯片有源面朝下對著印刷電路板,可以實現最短的電路徑,這也保證了更高的速度和更少的寄生效應。另一方面,由于采用批量封裝,整個晶圓能夠實現一次全部封裝,成本的降低也是晶圓級封裝的另一個推動力量。

2.INFO InFO(Integrated Fan-out)是臺積電(TSMC)于2017年開發出來的FOWLP先進封裝技術,是在FOWLP工藝上的集成,可以理解為多個芯片Fan-Out工藝的集成,而FOWLP則偏重于Fan-Out封裝工藝本身。 InFO給予了多個芯片集成的空間,可應用于射頻和無線芯片的封裝,處理器和基帶芯片封裝,圖形處理器和網絡芯片的封裝。下圖為FIWLP,FOWLP和InFO對比示意圖。