簡單介紹GaN功率器件的散熱,揭示GaN器件散熱瓶頸的原因。 還回顧了近年來國外發展起來的GaN功率器件芯片級先進散熱技術,系統總結分析了各項技術的散熱機理、設計方案、工藝途徑和研究進展,闡述了芯片級先進散熱技術的原理和技術現狀及發展方向。

1 GaN 功率器件的熱瓶頸

盡管 GaN 功率器件具有極高的輸出功率能力,但現階段的應用(主要為 GaN HEMT 和功放 MMIC)因其熱效應問題導致輸出功率密度僅在 3~5 W/mm,遠低于其實驗室驗證的 42 W/mm,可以看出,GaN 半導體特有的大功率性能優勢遠未充分發揮。這是由于 GaN 功率器件在工作時其溝道區域內不可避免地產生熱功耗,這種內熱功耗的積累導致芯片的結溫升高,在高源漏偏置電壓下器件就會出現輸出特性衰減現象,被定義為“自熱效應”,其功率密度越大,“自熱效應”越明顯。因此,如何解決其溝道區熱功耗積累問題是提升其功率特性的主要途徑。

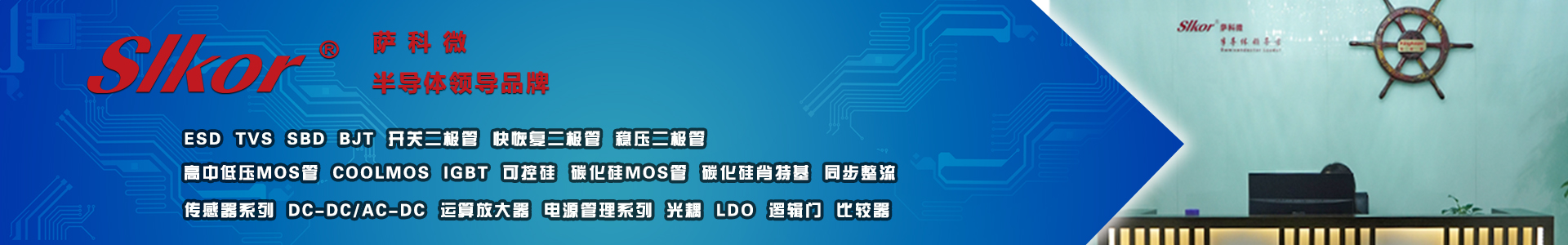

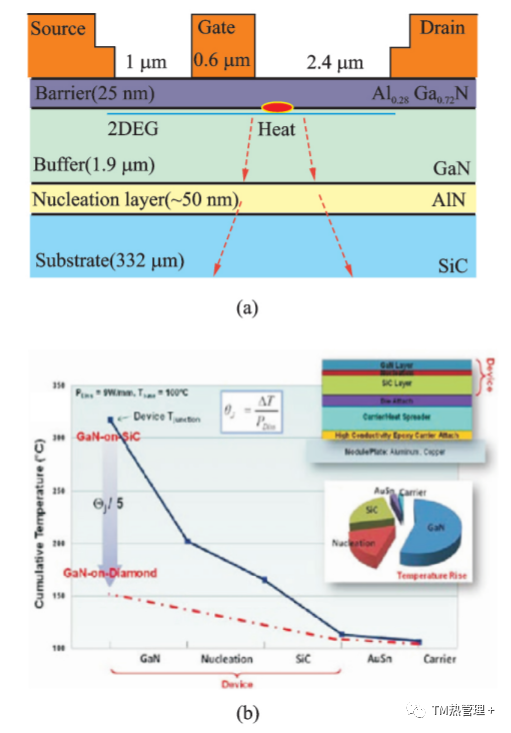

通常在 GaN 半導體微波功率器件中,其溝道區位于芯片有源區的源漏位置下端區域,其熱功耗的集中主要在溝道區的柵位置下端偏漏區域,其尺寸一般小于1 μm,只占整個半導體芯片面積的極小的部分,即功耗的集中區即為熱源區,如圖 1(a)所示。

針對傳統的 SiC 襯底 GaN 器件,其工作時熱源區的熱量主要是通過芯片內部的 GaN 外延層、SiC 襯底層傳遞至芯片封裝的熱沉上進行耗散,依據 DARPA 的研究若將芯片和封裝熱沉作為一個整體,其芯片內部的熱傳遞熱阻占整體傳熱熱阻的 50%以上,如圖1(b)所示。

圖1 GaN 器件熱瓶頸:(a)熱源區結構;(b)熱分布示意圖

SiC 襯底和 GaN 外延材料本身導熱能力所限制,該結果也表明即便封裝級的散熱能力極好,也難以解決其芯片在大功率條件下的有源區熱積累。因此,如何提升 GaN 芯片內部的熱傳遞能力,尤其是熱源區附近的傳熱能力成為解決其功率器件熱瓶頸和實現大功率特性的關鍵途徑。

由于 GaN 芯片的微納結構尺度和電路的功能性導致其芯片級的散熱技術開發極為困難,國際上在電子器件熱管理領域的開發上升至芯片層級的系統研究最早是在 2011 年,由美國 DARPA 進行頂層的項目設計和牽引支助,其目的解決 GaN 器件的熱瓶頸問題。從目前各研究結構報道的技術途徑來講,主要分為兩類:一是將高導熱材料與芯片片內的熱源區進行集成,增大芯片內部的熱傳遞能力,有效抑制熱積累,屬于被動散熱技術;二是將液體引入芯片內部的熱源區附件,通過和液體的熱交換,有效將熱源區的熱量帶走,該技術屬于主動散熱技術。主動散熱和被動散熱途徑因結構設計和工藝開發的不同分為以下四大類。

金剛石襯底 GaN 器件散熱技術最開始源于 2011年 DARPA 啟動的 NJTT(Near-junction thermal transport)熱管理項目,其概念是利用高熱導率的金剛石材料替換傳統 GaN 大功率器件的 SiC 襯底,增大其芯片內部的熱傳輸能力,旨在使其輸出功率密度達到傳統的芯片 3 倍以上,解決 GaN 近結區的熱積累,提升其器件的大功率特性和可靠性,被認為是下一代的 GaN 器件的[敏感詞]選擇。

然而該技術的實現依然面臨挑戰,主要包含三個方面:1)從原有襯底上將 GaN 外延層進行高質量、完整性的剝離技術;2)在 GaN 外延層上進行 100 μm 的金剛石襯底生長或異質鍵合的技術;3)實現超低的生長或異質鍵合的界面熱阻 (GaN/Diamond)。

針對上述的技術挑戰,多組研發團隊開展深入研究,以求技術突破,目前主要有以下兩個途徑。

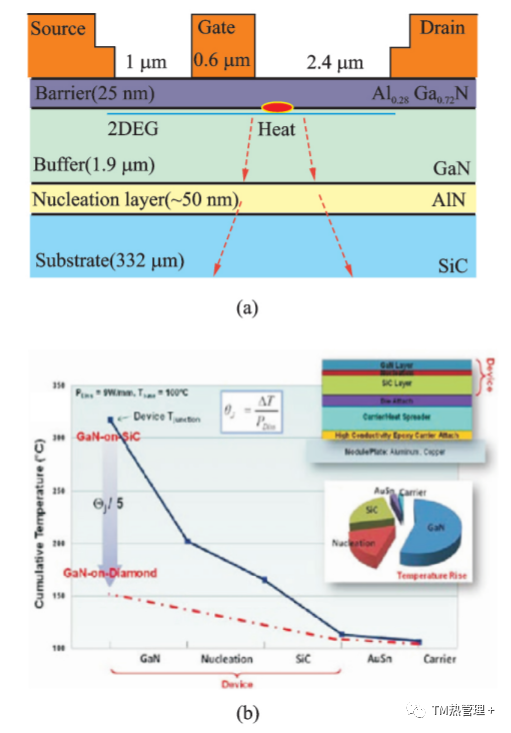

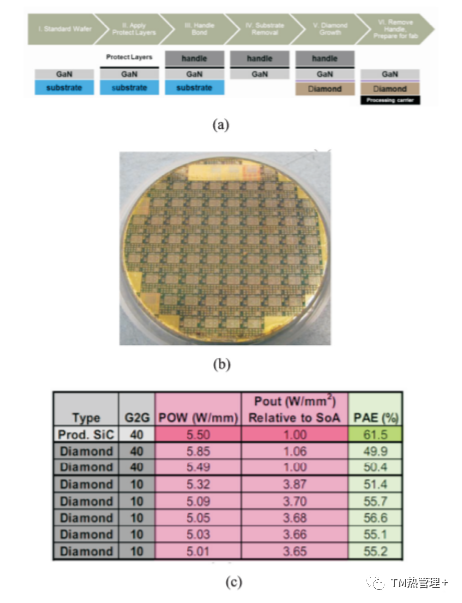

基于 GaN 外延生長金剛石技術。利用該技術實現金剛石襯底 GaN 器件是由 Raytheon 和 TriQuint 的研發團隊提出,其技術過程為利用 Si 基 GaN 外延層,采用臨時鍵合將 Si 襯底及其高界面熱阻層(GaN/Si)移除,隨后在 GaN 外延層上直接生長 100 μm 的金剛石多晶材料,實現金剛石襯底的 GaN 結構,如圖 2(a)和(b)所示。

圖2 金剛石襯底 GaN 直接生長技術:(a)工藝過程;(b)樣品;(c)散熱能力

該技術途徑開發難點是實現高質量的金剛石多晶的生長,其研發團隊采用 HFCVD 和 MPCVD 方式生長技術,并引入幾納米的過渡層,近而保證金剛石及其和 GaN 界面的質量,實現其襯底的高熱導和界面的低熱阻特性。

Raytheon 利用該技術成功研制出金剛石襯底 GaN HEMT,在 RF 模式下實現了 3.87 倍于傳統 SiC 襯底的 GaN 器件的功率密度[如圖2(c)所示],且其金剛石和界面熱阻可低至 29 m2K/GW。TriQuint 團隊也報道了其研究成果,在 DC 模式下,研制的金剛石襯底 GaN 晶體管的輸出功率是其傳統 SiC 襯底和 Si 襯底的 2.2 倍和 3.4 倍。

可以看出該技術在散熱能力方面體現出極為突出的優勢,但是無論 Raytheon 和 TriQuint 的研究結果都遇到了金剛石襯底 GaN 晶體管的高漏電現象,該現象導致低的增益和擊穿電壓,限制了其大功率高效能的應用。其研究報道顯示導致該現象的原因尚不完全清楚,但可以通過其工藝和結構的優化降低該漏電現象,且認為以 SiC 基 GaN 外延層制備生長的金剛石襯底 GaN 器件會有效提升該缺陷,是其研發團隊后續探索的問題。

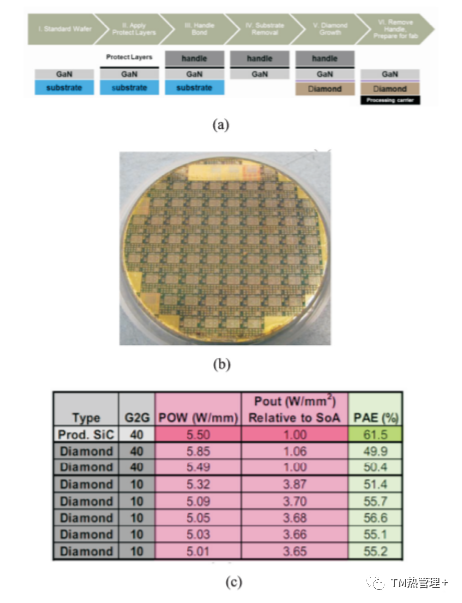

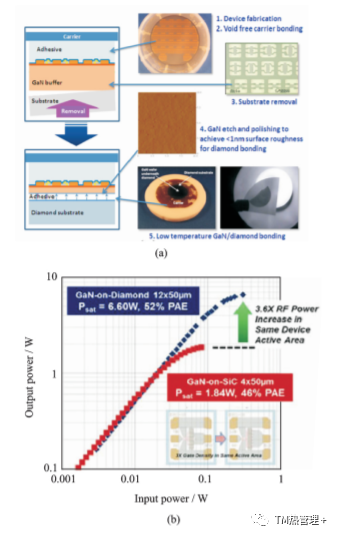

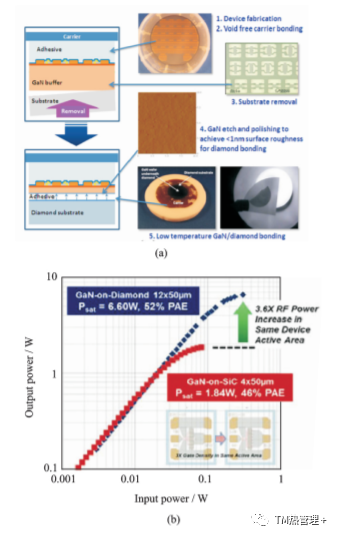

基于異質鍵合技術。利用該技術實現金剛石襯底 GaN 器件的途徑是由 BAE Systems 的研發團隊提出和開發,其技術過程為利用 SiC 基 GaN 外延層,采用臨時鍵合將 SiC 襯底及其界面熱阻層(GaN/SiC)移除,隨后利用異質鍵合的技術將 GaN 外延層和金剛石多晶襯底進行直接粘接,近而實現金剛石襯底的 GaN 結構,如圖 3(a)所示。

圖3 金剛石襯底 GaN 異質鍵合技術:(a)工藝過程;(b)散熱能力

該技術途徑開發難點是實現低溫、高質量界面的異質鍵合工藝開發,其研發團隊采用的是在 GaN 外延層和金剛石襯底上分別蒸發粘接介質,在特定的工藝條件下進行異質鍵合,為了保證其鍵合質量,其兩個鍵合面的粗糙度要求小于 1nm,其鍵合過程中的溫度可低至 150℃,充分保證了該技術和器件制備技術的兼容性,但是其鍵合工藝和鍵合介質并未報道。

依據上述的設計途徑, BAE Systems 成功研制出金剛石襯底 GaN HEMT,如圖 3(b)所示,實現了 11W/mm 的 RF 輸出功率密度,是該結構下傳統 SiC 襯底 GaN 器件的總輸出功率密度的 3.6 倍。

該技術優勢是其金剛石襯底可以單獨制備,有效保證其金剛石襯底的高導熱特性,但其散熱能力嚴重受鍵合界面層的質量影響,其最小值可達 35 m2 K/GW,相對于直接生長技術,該界面熱阻較高,也是后續該技術的研究重點。

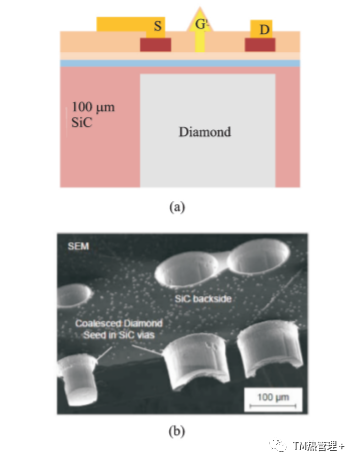

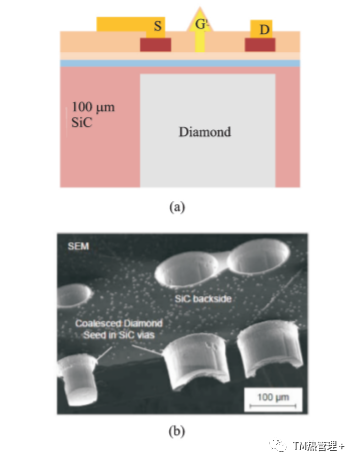

金剛石嵌入式散熱柱技術也是基于 NJTT 熱管理項目,其概念是將高熱導率的金剛石材料嵌入到 GaN 器件有源區下端的 SiC 襯底的中,使金剛石接近熱源端,使熱源區域熱量通過金剛石散熱柱有效熱擴散,進而解決 GaN 近結區的熱積累,其結構如圖4(a)所示。

該技術主要是由 Northrop Grumman AS 提出并進行探索開發,其技術路徑是利用 SiC 基 GaN 器件,在其有源區下端的區域對 SiC 襯底進行深度刻蝕,并采用生長的技術對刻蝕孔進行金剛石材料的生長,實現金剛石嵌入式散熱柱結構。

該散熱結構可以認為是金剛石襯底 GaN 散熱技術的一種妥協,不改變 SiC 襯底 GaN 的結構,僅在熱源區下端嵌入金剛石柱,可有效解決金剛石襯底 GaN 結構因整片轉移、異質鍵合或生長引起的 GaN 外延層的質量、界面熱阻及應力等技術問題。但從理論上分析該技術在散熱能力和效果上相對金剛石襯底 GaN 散熱結構有一定差距。

目前 Northrop Grumman AS 對該技術的實現工藝進行了開發,如圖4(b)所示,其關鍵技術是微米級刻蝕孔的金剛石散熱柱的生長,和美國 Naval Research Laboratory 合作開發了 MPCVD 的生長技術,采用種子層引晶生長途徑解決其高徑深比的金剛石柱生長問題,其金剛石和 SiC 襯底接觸區域的界面熱阻低至 9.5 m2 K/GW,金剛石散熱柱的熱導率高達 1350 W/mk,遠高于其 SiC 襯底的理論熱導率 490 W/mk。但是到目前為止,Northrop Grumman AS 并未有金剛石嵌入式散熱柱結構 GaN 器件的散熱試驗驗證報道。

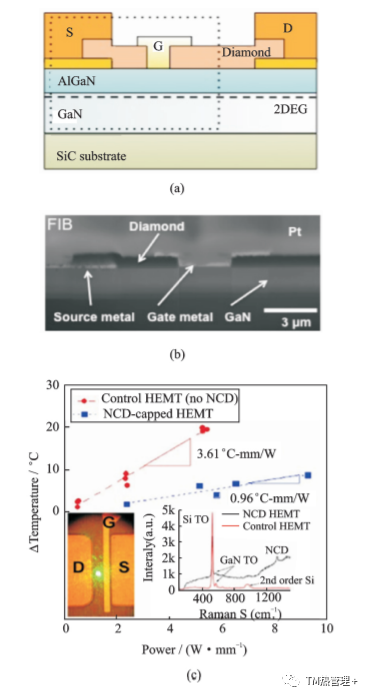

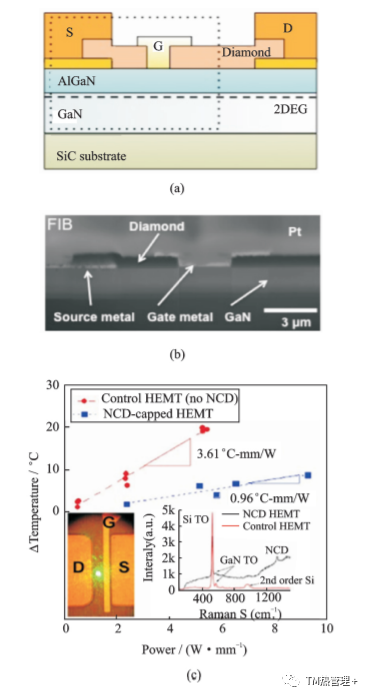

高導熱鈍化層散熱技術是由美國 Naval Research Laboratory 在 2012 年繼 DARPA 的實施的芯片級熱管理之后提出的,目的也是解決 GaN 器件熱積累,提升其大功率特性和高可靠性問題。其結構設計如圖 5(a)所示,是利用金剛石薄膜材料替換原有源區的傳統鈍化層 SiNx 材料,利用金剛石薄膜的高導熱特性,增加其熱源區的橫向熱傳遞能力,有效避免有源區的熱積累。

圖5 (a)熱設計結構;(b)制備工藝;(c)散熱能力

該技術的優勢是并不改變現有的 GaN 器件的制備技術,僅在現有的技術上增加高導熱薄膜鈍化工藝即可。該技術主要是由 Naval Research Laboratory 提出,并聯合 University of Bristol、Universiddad Politécnica de Madrid 及 Massachusetts Institue of Technology 等高校和研究機構共同探索開發,其采用的技術路徑是基于傳統的 Si 基 GaN 器件,在有源區的柵兩側采用 MPCVD 的生長技術進行納米級金剛石薄膜層的生長,實現高導熱鈍化層散熱結構,如圖 5(b)所示。并制備了對應的 GaN 器件,驗證實現了 10 W/mm 功率密度,在 5 W/mm 功率時該散熱結構比常規的 GaN 器件結溫降低 20%,隨著功率密度的增大其散熱優勢愈加明顯[如圖 5(c)所示]。與此同時,該研究團隊在該研究基礎上正在嘗試有源區整個柵結構也采用金剛石材料來制備,以求達到更為突出的散熱能力。

片內微流冷卻散熱技術源于 2013 年 DARPA 啟動的 ICECool(Intra-chip embedded cooling)熱管理項目,其概念是在芯片的襯底中直接制造微流道,將流體引入其中進行交換散熱。其目的是針對高性能大功率雷達和超級計算中心的發展應用,旨在提升其芯片的熱傳輸特性,使其滿足 1kW/cm2 的散熱能力。由于該技術的創新性和顛覆性極大,其微流道的設計、管控技術、及其工藝開發的途徑較多,因此 DARPA 支助的團隊較多,且每組團隊針對的技術問題和實現的途徑不同,目前,該技術的研究開發主要體現為以下三種:

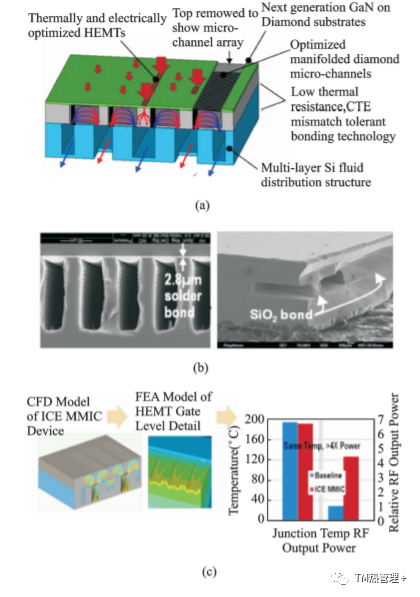

(1)基于 SiC 襯底的片內微流散熱技術。該技術途徑由 Lockheed Martin 研發團隊提出,其過程是在 SiC 襯底的內部刻蝕微流道,并采用單項流進行散熱,如圖6 所示。其技術管控途徑的設計是利用 SiC 襯底背面和熱沉的流道相結合的方式,使熱沉中的流體通過分流直接流經芯片熱源區域下端的 SiC 襯底,而內部流體則采用的是冷凍液,近而實現芯片近結區的高效熱交換冷卻的目的,如圖 6(a)所示。該技術途徑的難點是熱沉中微流道和襯底中微流道的協同設計和微流體的管控,針對該技術難點的控制報道中并未詳細說明。同時該團隊基于射頻功率器件,將該技術進行了 GaN MMIC 的應用驗證研究,滿足其熱源區域的熱流密度達 30 kW/cm2,芯片的熱流密度達1 kW/cm2 的目的,達到了5倍于同等結構芯片的熱流密度,實現了在同等功率條件下熱阻降低四倍的效果,如圖 6(b)所示。該技術的研究主要是減少射頻功率器件的近結溫度,提升其性能、壽命和可靠性。

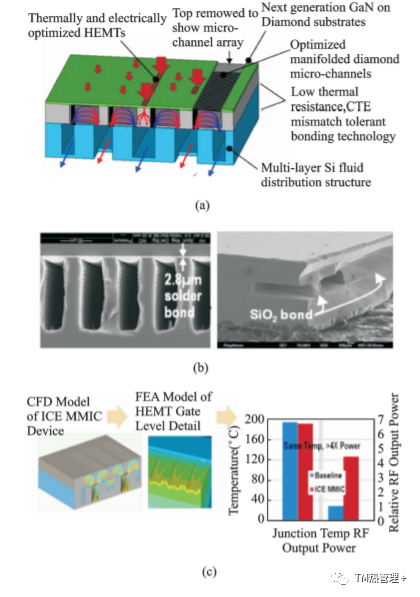

(2)基于金剛石襯底的片內微流散熱技術。該技術途徑由 Raytheon 研發團隊提出,其技術途徑設計為在 GaN 器件柵區下端的近結區的金剛石襯底中進行刻蝕微流道,并采用硅襯底進行鍵合密封和微流管控,微流體通過硅襯底的分流進入芯片的金剛石襯底有源區熱源附近直接進行熱交換散熱,如圖所示 7(a)所示。其金剛石襯底和硅襯底的互連采用了兩種技術途徑,如圖 7(b)所示,[敏感詞]種途徑是利用焊料進行焊接密封,焊接層約 2.8 μm,可充分保證其微流道的密封性和結合強度,但存在鍵合焊接應力問題;第二種途徑采用氧化物鍵合方式,報道中利用的鍵合層是 SiO2 材料,充分解決了異質鍵合的應力問題,但存在鍵合熱阻相對較大問題;其上的兩種技術方案均采用晶圓級鍵合,有效保證后續量產的生產線的工藝統一性。該團隊也利用了有限元仿真模型對該片內微流冷卻技術的散熱能力進行了計算評估,如圖 7(c)所示,結果表明保持相同的結溫,該片內微流散熱的結構其功率輸出能力較傳統同結構輸出增大 4 倍以上。但是該仿真評估結果還未得到相關報道試驗的驗證,也可能是該設計方案難度相對較高引起,目前該技術開發依然以其工藝實現的探索為主。

圖7 (a)熱設計結構;(b)制備工藝;(c)散熱能力

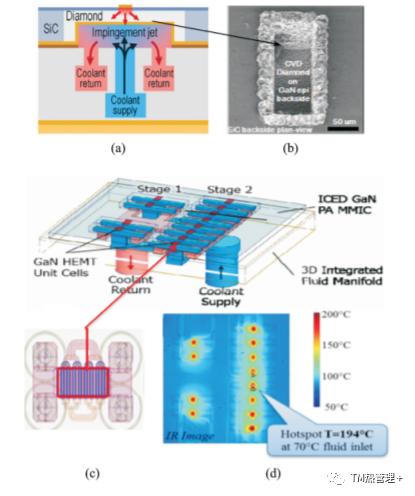

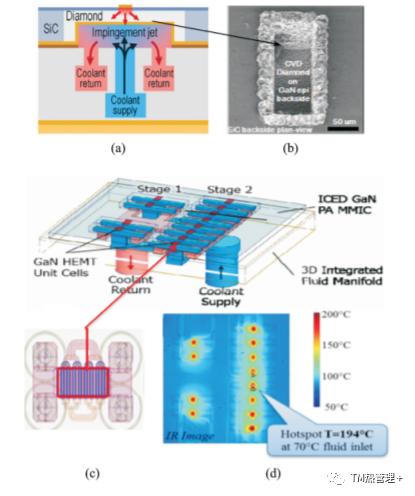

(3)基于散熱柱的片內微流散熱技術。該技術途徑主要由 Northrop Grumman AS 研發團隊提出,如圖 8(a)所示,采用的是雙散熱結構模式,基于金剛石嵌入式散熱柱結構的散熱模式上再次進行片內微流的熱交換散熱技術開發。其技術過程為先將在金剛石散熱柱嵌入到 GaN 器件有源區下端的 SiC 襯底中,再利用刻蝕工藝對金剛石散熱柱進行微流道制備,如圖 8(b)所示;其特點是一個有源區對應一個微流道,中心位置為微流進口,兩邊位置為微流出口,微流道的尺寸遠大于其有源區尺寸,并采用硅襯底進行鍵合密封和實現微流管控,其原理是微流體通過硅襯底的入口后進行分流至芯片的金剛石襯底有源區熱源附近直接進行熱交換散熱,如圖 8(c)所示。該設計方案的難點是片內嵌入金剛石材料存在界面(金剛石/SiC)熱阻控制問題,對金剛石的生長工藝要求較高,同時芯片內嵌金剛石的 SiC 襯底和硅基襯底的密封采用是焊料鍵合方式,涉及三種異質材料的焊接,其封接層的應力控制也是其難點之一。與此同時,該團隊的研究進展較為突出,基于 GaN HEMT 實現了設計結構的散熱能力驗證,如圖 8(d)所示,其熱源區域的熱流密度高達達 30 kW/cm2,實現4倍于傳統芯片的 RF 功率輸出,且該團隊報道其設計、工藝開發及驗證在進一步的改進優化中。

圖8 (a)熱設計結構;(b)制備工藝;(c)器件結構;(d)散熱能力

以美國DARPA開展的NJTT和ICEColl項目為代表,通過對其散熱技術的探索和研究進行詳細分析,可以看出目前的技術發展主要是基于材料與材料集成的研究。導熱性高。 在芯片內部,體現在采用金剛石作為GaN的芯片襯底、散熱柱、鈍化層等近結散熱技術工藝成熟度較高。 目前已有部分研究通過匹配GaN產品得到驗證。 在RF模式下,實現了傳統SiC襯底3.87倍的[敏感詞]GaN的功率密度。

片上微通量冷卻散熱技術在實現高功率密度器件方面具有重大顛覆性意義,在熱源區GaN MMIC實現了30 kW/c㎡的熱流密度,是熱流密度的5倍具有相同結構的傳統芯片。 其應用成熟度較低,在片上微流控結構設計、微流控控制、器件應用的集成兼容性方面仍存在差異。 盡管如此,該技術在大功率GaN器件中的先天優勢和發展潛力仍備受關注,將是未來芯片級熱管理的重要發展方向。

免責聲明:本文采摘自網絡,本文僅代表作者個人觀點,不代表薩科微及行業觀點,只為轉載與分享,支持保護知識產權,轉載請注明原出處及作者,如有侵權請聯系我們刪除。