服務(wù)熱線

0755-83044319

發(fā)布時(shí)間:2022-03-18作者來源:薩科微瀏覽:2285

如果有人跟你說:“嗨,我做的芯片實(shí)現(xiàn)了100%自主可控!”等等,你先不急著崇拜(相信)他,請看完此文再說...

01

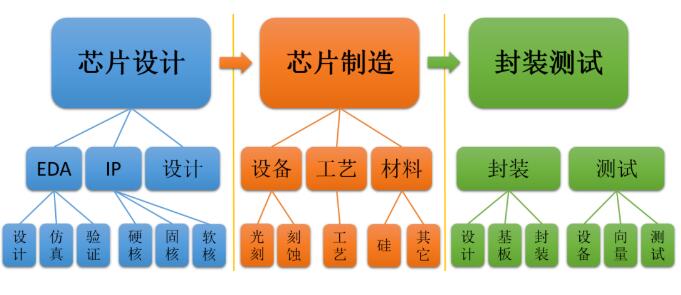

芯 片 設(shè) 計(jì)

1.1 EDA

EDA(Electronic Design Automation)電子設(shè)計(jì)自動化,常指代用于電子設(shè)計(jì)的軟件。

曾經(jīng)有人跟我說:“EDA有啥呀,不就是個(gè)工具嘛?”是啊,確實(shí)就是個(gè)工具,可是沒這個(gè)工具,你啥也設(shè)計(jì)不了啊!

現(xiàn)在的大規(guī)模集成電路在芝麻粒大小的1平方毫米內(nèi)可以集成1億只以上的晶體管,這些晶體管之間的連接網(wǎng)絡(luò)更是多達(dá)數(shù)億個(gè)。當(dāng)今主流的SoC芯片,其晶體管數(shù)量已經(jīng)超過百億量級。如果沒有精準(zhǔn)的,功能強(qiáng)大的EDA工具,怎么設(shè)計(jì)呢?

EDA是芯片設(shè)計(jì)的必備工具,目前,Synopsys、Cadence和Mentor(Siemens EDA)占據(jù)著超過90%以上的市場份額。在10納米以下的高端芯片設(shè)計(jì)上,其占有率甚至高達(dá)100%。也就是說,現(xiàn)在研發(fā)一款10nm以下的芯片,沒有以上三家的EDA工具幾乎是不可能實(shí)現(xiàn)的。

下表所示是目前芯片設(shè)計(jì)中主流的EDA工具:

1.2 IP

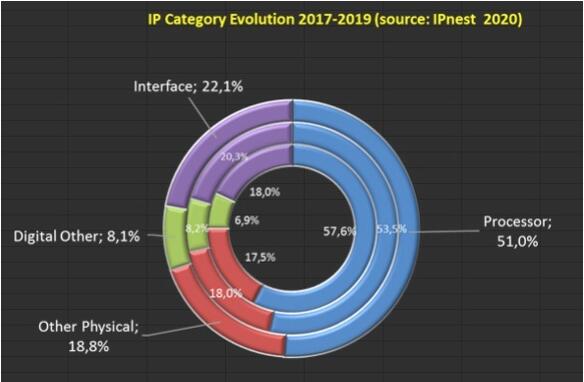

下表為目前全球前10大IP提供商,可以看到中國有兩家入圍前十,但是兩家市場份額加起來也僅有3%,而ARM一家就占據(jù)了40%以上的市場份額,美國的企業(yè)則占據(jù)了30%的市場份額,如果ARM被英偉達(dá)收購,基本上IP市場就是美國的天下了。此外我們也發(fā)現(xiàn),全球[敏感詞]的兩家EDA公司Synopsys和Cadence,在IP領(lǐng)域也同樣占據(jù)的第二、第三的位置。

下圖所示為IP的種類,其中處理器占51%,接口IP占22.1%,數(shù)字類占8.1%,其他占18.8%,處理器類ARM一家獨(dú)大,在接口類IP中,Synopsys是業(yè)界領(lǐng)導(dǎo)者。

我們需要考慮的是,在設(shè)計(jì)的芯片中那些IP是自主設(shè)計(jì)的,那些是外購的,這些外購的IP是否存在不可控因素?如果你設(shè)計(jì)的SoC僅僅是把別人的IP打包整合,那自主可控性就要大打折扣了。

下面,我們以華為麒麟980為例,了解一下芯片研發(fā)中的IP使用情況。

麒麟980芯片集成的主要部件有CPU、GPU(俗稱顯卡)、ISP(處理拍照數(shù)據(jù))、NPU(人工智能引擎)和基帶(負(fù)責(zé)通信)。

根據(jù)華為官方資料,ISP是華為自研,NPU是華為和寒武紀(jì)合作的成果,至于CPU(Cortex-A76)和GPU(Mali-G76)則是華為向ARM公司購買的授權(quán),包括指令集授權(quán)和內(nèi)核授權(quán)。

如果沒有IP授權(quán),還有沒有可能自研麒麟980芯片,目前看來,沒有 。

1.3 設(shè)計(jì)流程

芯片設(shè)計(jì)流程通常可分為:數(shù)字IC設(shè)計(jì)流程和模擬IC設(shè)計(jì)流程。

數(shù)字IC設(shè)計(jì)流程:芯片定義 → 邏輯設(shè)計(jì) → 邏輯綜合 → 物理設(shè)計(jì) → 物理驗(yàn)證 → 版圖交付。

芯片定義(Specification)是指根據(jù)需求制定芯片的功能和性能指標(biāo),完成設(shè)計(jì)規(guī)格文檔。

邏輯設(shè)計(jì)(Logic Design)是指基于硬件描述語言在RTL(Register-Transfer Level)級實(shí)現(xiàn)邏輯設(shè)計(jì),并通過邏輯驗(yàn)證或者形式驗(yàn)證等驗(yàn)證功能正確。

邏輯綜合(Logic Synthesis)是指將RTL轉(zhuǎn)換成特定目標(biāo)的門級網(wǎng)表,并優(yōu)化網(wǎng)表延時(shí)、面積和功耗。

物理設(shè)計(jì)(Physical Design)是指將門級網(wǎng)表根據(jù)約束布局、布線并最終生成版圖的過程,其中又包含:數(shù)據(jù)導(dǎo)入 → 布局規(guī)劃 → 單元布局 → 時(shí)鐘樹綜合 → 布線。

數(shù)據(jù)導(dǎo)入是指導(dǎo)入綜合后的網(wǎng)表和時(shí)序約束的腳本文件,以及代工廠提供的庫文件。

布局規(guī)劃是指在芯片上規(guī)劃輸入/輸出單元,宏單元及其他主要模塊位置的過程。

單元布局是根據(jù)網(wǎng)表和時(shí)序約束自動放置標(biāo)準(zhǔn)單元的過程。

時(shí)鐘樹綜合是指[敏感詞]時(shí)鐘緩沖器,生成時(shí)鐘網(wǎng)絡(luò),最小化時(shí)鐘延遲和偏差的過程。

布線是指在滿足布線層數(shù)限制,線寬、線間距等約束條件下,根據(jù)電路關(guān)系自動連接各個(gè)單元的過程。

物理驗(yàn)證(Physical Verificaiton)通常包括版圖設(shè)計(jì)規(guī)則檢查(DRC),版圖原理圖一致性檢查(LVS)和電氣規(guī)則檢查(ERC)等。

版圖交付(Tape Out)是在所有檢查和驗(yàn)證都正確無誤的前提下,傳遞版圖文件給代工廠生成掩膜圖形,并生產(chǎn)芯片。

模擬IC設(shè)計(jì)流程:芯片定義 → 電路設(shè)計(jì) → 版圖設(shè)計(jì) → 版圖驗(yàn)證 → 版圖交付。

其中芯片定義和版圖交付和數(shù)字電路相同,模擬IC在電路設(shè)計(jì)、版圖設(shè)計(jì)、版圖驗(yàn)證和數(shù)字電路有所不同。

模擬電路設(shè)計(jì)是指根據(jù)系統(tǒng)需求,設(shè)計(jì)晶體管級的模擬電路結(jié)構(gòu),并采用SPICE等仿真工具驗(yàn)證電路的功能和性能。

模擬版圖設(shè)計(jì)是按照設(shè)計(jì)規(guī)則,繪制電路圖對應(yīng)的版圖幾何圖形,并仿真版圖的功能和性能。

模擬版圖驗(yàn)證是驗(yàn)證版圖的工藝規(guī)則、電氣規(guī)則以及版圖電路圖一致性檢查等。

這里,我們做一個(gè)簡單的總結(jié):

芯片設(shè)計(jì):就是在EDA工具的支持下,通過購買IP授權(quán)+自主研發(fā)(合作開發(fā))的IP,并遵循嚴(yán)格的集成電路設(shè)計(jì)仿真驗(yàn)證流程,完成芯片設(shè)計(jì)的整個(gè)過程。在這個(gè)過程中,EDA、IP、嚴(yán)格的設(shè)計(jì)流程三者缺一不可。

目前看來,在這三要素中最先可能實(shí)現(xiàn)自主可控的就是設(shè)計(jì)流程了。

下表列出了當(dāng)前世界前10的芯片設(shè)計(jì)公司,供大家參考。

02

芯 片 制 造

2.1 設(shè)備

芯片制造中,有三大關(guān)鍵工序:光刻、刻蝕、沉積。三大工序在生產(chǎn)過程中不斷重復(fù)循環(huán),最終制造出合格的芯片。

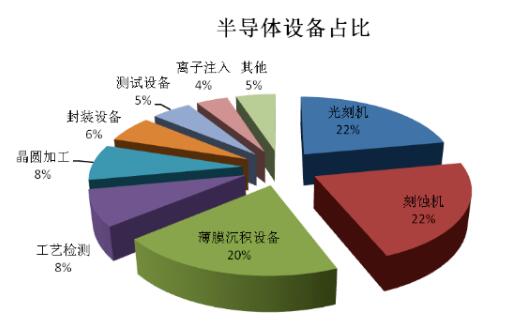

三大關(guān)鍵工序要用到三種關(guān)鍵設(shè)備,分別是光刻機(jī)、刻蝕機(jī)、薄膜沉積設(shè)備。三大設(shè)備占所有設(shè)備投入的22%、22%、20%左右,是三種占比[敏感詞]的半導(dǎo)體設(shè)備。

光刻機(jī)

免責(zé)聲明:本文轉(zhuǎn)載自“芯論語”,本文僅代表作者個(gè)人觀點(diǎn),不代表薩科微及行業(yè)觀點(diǎn),只為轉(zhuǎn)載與分享,支持保護(hù)知識產(chǎn)權(quán),轉(zhuǎn)載請注明原出處及作者,如有侵權(quán)請聯(lián)系我們刪除。

公司電話:+86-0755-83044319

傳真/FAX:+86-0755-83975897

郵箱:1615456225@qq.com

QQ:3518641314 李經(jīng)理

QQ:332496225 丘經(jīng)理

地址:深圳市龍華新區(qū)民治大道1079號展滔科技大廈C座809室

友情鏈接:站點(diǎn)地圖 薩科微官方微博 立創(chuàng)商城-薩科微專賣 金航標(biāo)官網(wǎng) 金航標(biāo)英文站

Copyright ?2015-2022 深圳薩科微半導(dǎo)體有限公司 版權(quán)所有 粵ICP備20017602號-1