服務(wù)熱線

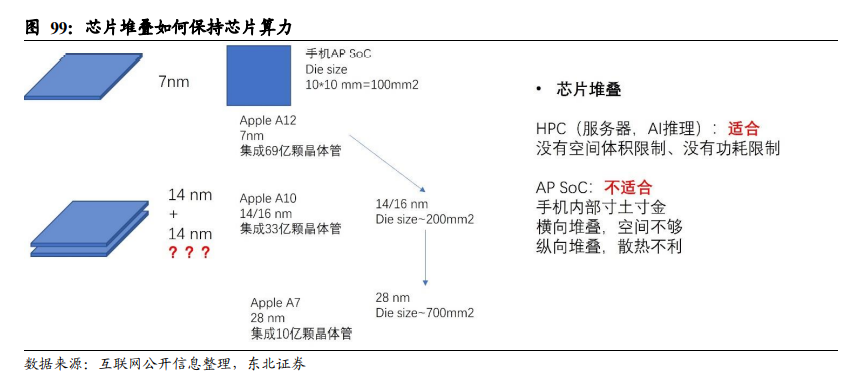

0755-83044319

發(fā)布時間:2023-02-14作者來源:薩科微瀏覽:1941

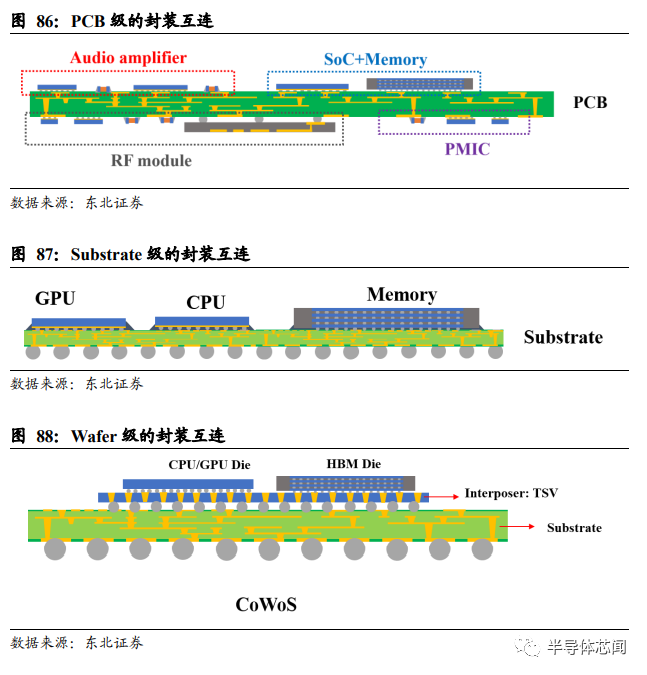

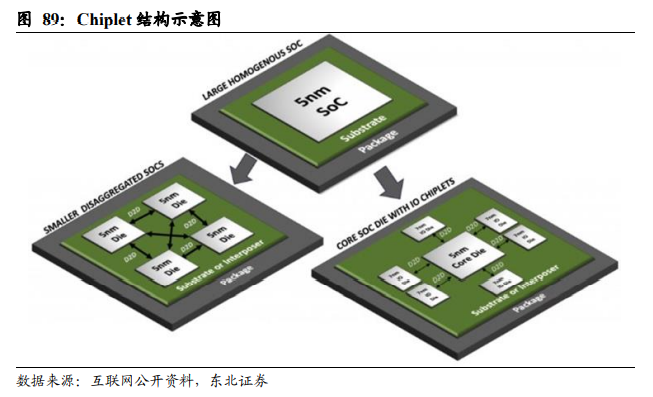

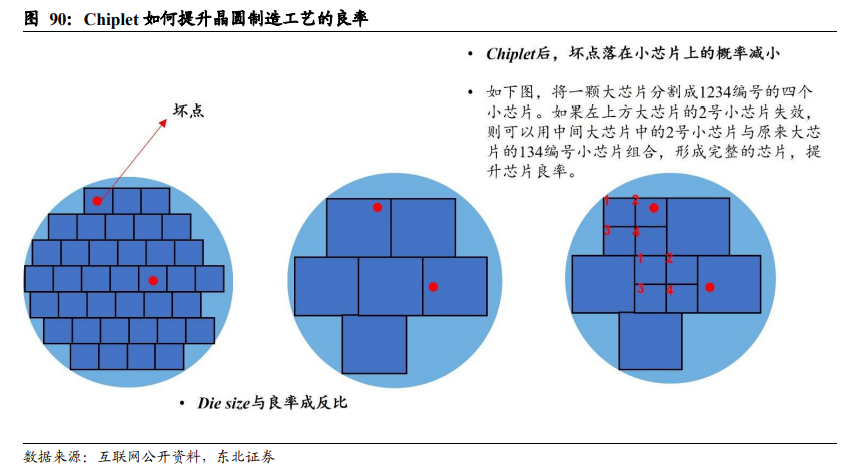

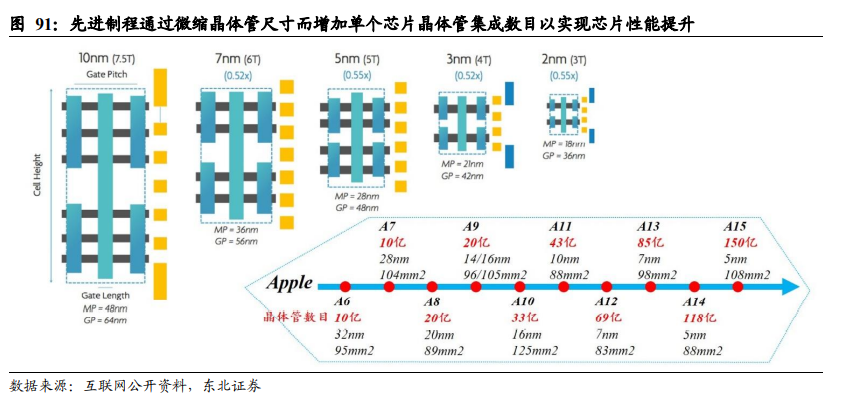

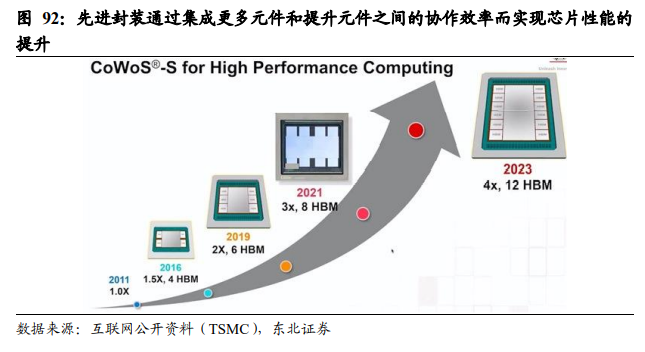

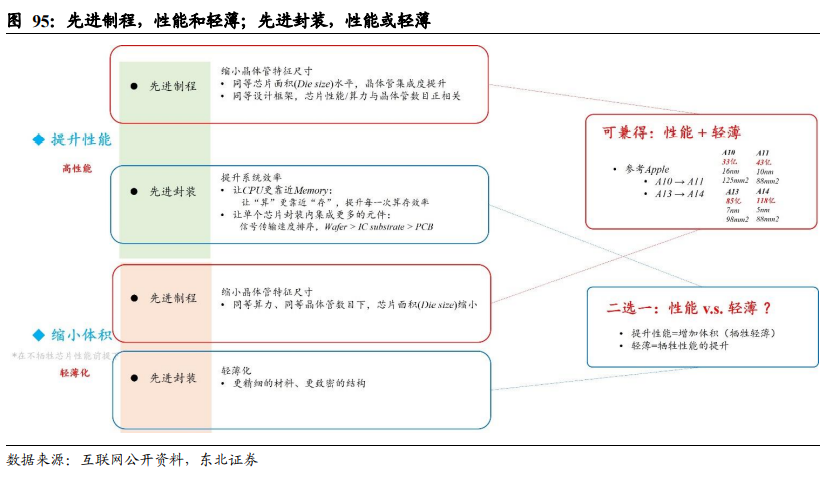

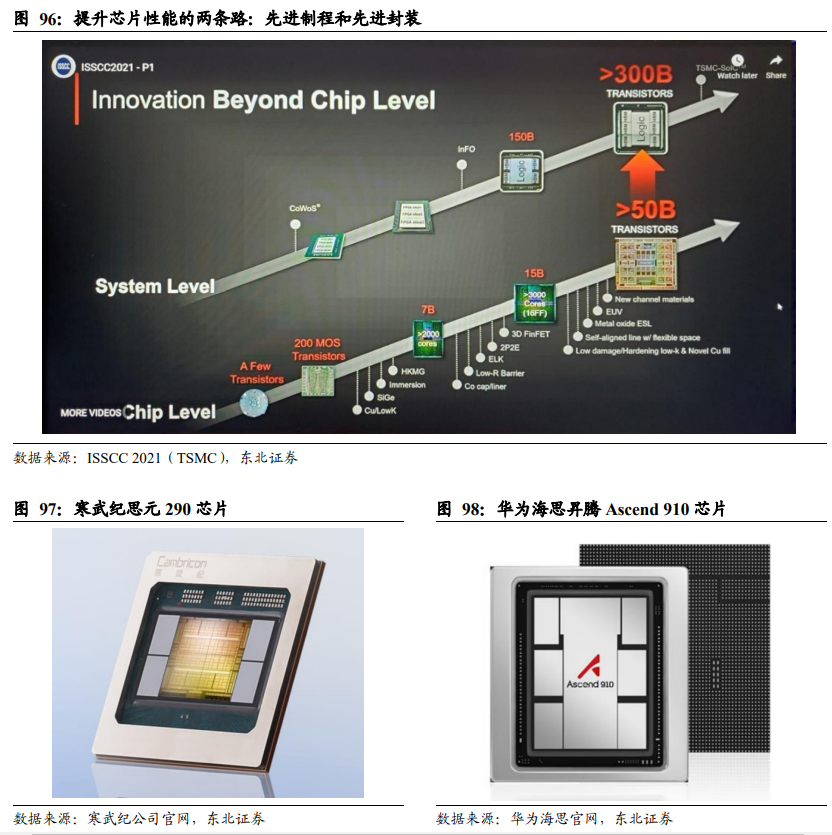

1. 先進(jìn)制程受限,先進(jìn)封裝/Chiplet提升算力,必有取舍

2. 大功耗、高算力的場景,先進(jìn)封裝/Chiplet有應(yīng)用價值

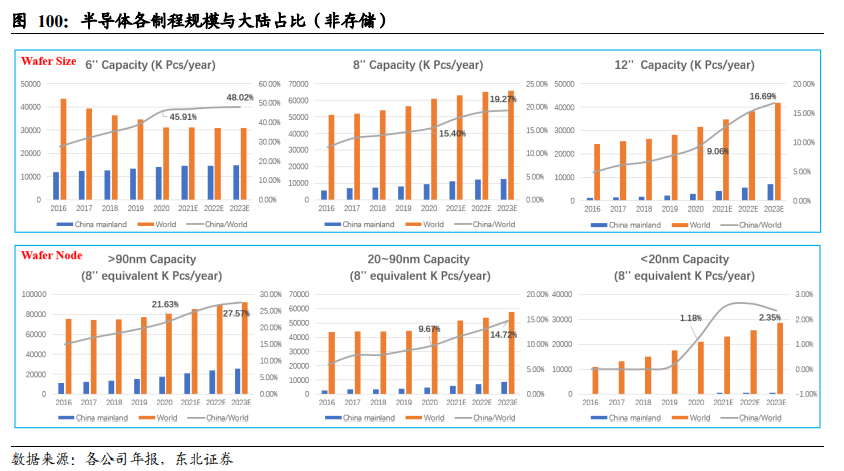

3. 我國先進(jìn)制程產(chǎn)能儲備極少,先進(jìn)封裝/Chiplet有助于彌補(bǔ)制程的稀缺性

友情鏈接:站點(diǎn)地圖 薩科微官方微博 立創(chuàng)商城-薩科微專賣 金航標(biāo)官網(wǎng) 金航標(biāo)英文站

Copyright ?2015-2022 深圳薩科微半導(dǎo)體有限公司 版權(quán)所有 粵ICP備20017602號-1