從集成電路設計產業(yè)技術發(fā)展趨勢出發(fā),討論了IP核相關技術和特有的發(fā)展模式。從國內外的市場和技術發(fā)展趨勢出發(fā),針對先進工藝技術支持的高端芯片和特色工藝支持的成熟芯片需要的IP做了分析,簡要地介紹了先進設計和制造協(xié)同優(yōu)化和人工智能技術在IP驗證中的應用。最后提出了發(fā)展我國集成電路設計中IP技術和產業(yè)的策略以及建議。

集成電路產業(yè)是信息技術產業(yè)的核心,是支撐經(jīng)濟社會發(fā)展和保障國家安全的戰(zhàn)略性、基礎性和先導性產業(yè)。《國家集成電路產業(yè)發(fā)展推進綱要》對產業(yè)3大特征的定位主要體現(xiàn)在:(1)我國近幾年每年集成電路進口額巨大,2017年達到2601億美元(海關[敏感詞]數(shù)據(jù)顯示2018年達3120.58億美元),遠高于原油或其他戰(zhàn)略物質進口總額;(2)產業(yè)的發(fā)展高度依賴于材料、機械(裝備)、電子和軟件等基礎工業(yè)的支撐;(3)[敏感詞]的先導技術研發(fā)成果通常在集成電路產業(yè)中首先得到應用,從而引導其他產業(yè)的發(fā)展方向。芯片的重要性如同[敏感詞]次、第二次工業(yè)革命中的蒸汽機和內燃機。無論是日常生活的手機、電腦,還是企業(yè)應用的服務器與數(shù)據(jù)中心、工業(yè)機器人,乃至航空航天和[敏感詞]安全都離不開芯片。

芯片設計中的IP核(intellectual property core,IP)通常指應用在系統(tǒng)芯片(SoC)中且具有特定功能的可復用(reusable)的電路模塊,具有標準性和可交易性。通過產業(yè)化驗證的IP電路模塊可以被系統(tǒng)設計工程師直接植入芯片。IP包括CPU類(包括DSP、MPU、MCU),已經(jīng)成為集成電路設計技術的核心與精華。IP大體上可以分為軟核(soft core)、硬核(hard core)和固核(firm core)3種。

IP軟核是獨立于制造工藝的寄存器傳輸級(RTL)代碼,經(jīng)過行為級(behavioral)的功能驗證(functional verification)和優(yōu)化,使用時具有相當?shù)撵`活度。IP硬核是通過系統(tǒng)設計驗證、物理版圖設計驗證和工藝制造獲得的半成品或者產品。其優(yōu)點是確保電路性能達到設計目標,提交形式是芯片制造掩模版結構的全部版圖和詳細系統(tǒng)的全套工藝相關文件。由于與成套工藝的綁定 ,硬核沒有應用靈活度。工藝升級后相應的硬核需要重新驗證、重新進行物理設計。在軟核與硬核之間的是IP固核。固核通常以邏輯門級網(wǎng)表(gate-level netlist)的形式提交。由于固核多由設計客戶完成最終布線設計,因此核的端口位置、核的形狀和大小都可以調整,比硬核更具有靈活度。

一個可復用的IP核必須要具備完整的系統(tǒng)設計與應用參數(shù)(specifications)說明,各種兼容的應用模型、可配置性、驗證代碼和測試文件,通用的總線接口以及通用的檢測接口,功能驗證、邏輯綜合和物理設計驗證等相關的腳本(script)文件、設計和轉讓文檔等。

從IP設計的產品類型來看,可以分為:(1)IP成熟產品模塊類。可以直接集成應用,例如DDR裸片等,也稱作已知合格芯片(known good die,KGD);(2)IP半成熟產品模塊類,也稱作驗證IP(簡稱VIP),IP設計者需要提供驗證代碼 ,供系統(tǒng)芯片(SoC)統(tǒng)一集成使用;(3)新定義或者新開發(fā)的,并且需要設計的IP(design IP,DIP)。VIP的類型有:高速IP類的 ,例如總線和接口標準(peripheralcomponent interface express,PCIe)、快速接口(rapi-dIO)等。DIP的類型有:人工智能專用DIP,大數(shù)據(jù)用DIP,物聯(lián)網(wǎng)(IoT)用DIP等。

根據(jù)IP核在SoC中的集成方式及應用場景,還可以將其分為:(1)接口IP,例如通用串行總線(universal serial bus ,USB)、串行高級技術附件(serial advanced technology attachment,SATA)、PCIe、高清多媒體接口/顯示端口(high definition multimediainterface,HDMI/Display Port,DP)等;(2)存儲IP,例如靜態(tài)隨機存取存儲器(SRAM)、動態(tài)隨機存取存儲器(DRAM),NAND/NOR閃存存儲器 、單次/多次可編程(OTP/MTP)存儲器等;(3)功能性IP,例如模數(shù)/數(shù)模轉換器(ADC/DAC)、數(shù)字信號處理器(DSP)、微控制器(MCU)、音視頻交叉存取(audiovideo interleave / interleaved,AVI)等IP。

隨著集成電路產業(yè)的工藝技術的發(fā)展,IC設計的性能不斷提升,復雜度不斷增加,很多IC的規(guī)模已經(jīng)達到10?~101?個晶體管,如圖1所示,從而對IP的驗證提出了更高、更快、更準確的要求。現(xiàn)有的以及不斷發(fā)展的驗證方法已經(jīng)顯示出,設計規(guī)模越大,驗證時間越長,驗證覆蓋率的增大變得更困難,如圖2所示,這直接影響到IP或IC產品的性能等指標的收斂,影響設計可靠性(design for reliability,DFR),同時間接地影響到產品的量產(成本),也稱作設計量產性(designfor yield,DFY)。

圖2.IC/IP設計規(guī)模和復雜度的增加與驗證準確度的關系

集成電路產業(yè)的最上游是設計IP,2018年全球IP市場規(guī)模約49億美元。IP本身的產值雖然不是[敏感詞]但是其具有極大的附加值和特有的產業(yè)生態(tài)支柱作用 ,同時其產品與國家信息安全密切相關。以IP核復用為基礎的SoC技術是全球集成電路發(fā)展的方向。產業(yè)界以IP核設計為主的SoC占總數(shù)的90%以上。全球的10大設計IP的供應商如表1所示。

全球IP核龍頭企業(yè)ARM從2007年33%的市場占有率增加到2017年的46.2%,表明IP正向高度集中的方向發(fā)展。全球IP的發(fā)展路徑主要由上升中的SoC市場驅動。同時,開源CPU指令集(instructionset architecture,ISA)架構 RISC-V、人工智能的技術滲透和物聯(lián)網(wǎng)(IoT)推動的接口類IP是未來IP發(fā)展的熱點趨勢。例如,將多種傳統(tǒng) CPU、GPU、DSP 等模塊集成在同一個芯片的異構系統(tǒng)架構(heterogeneous system architecture,HSA)的設計中,美國[敏感詞]部先進研究項目局(DARPA)關注的、[敏感詞]提出的未來領域特定體系架構(domain specific architecture,DSA)等都將對IP的發(fā)展帶來新的應用需求。

隨著全球產業(yè)發(fā)展,處理器IP市場將占據(jù)[敏感詞]市場份額。由于對各種垂直領域的微處理器(MPU)、微控制器(MCU)、數(shù)字信號處理器(DSP)和圖形處理單元(GPU)的需求增加,處理器IP將占據(jù)半導體IP市場的[敏感詞]份額。其中,以移動通信微處理器龍頭企業(yè)ARM為代表的IP核授權業(yè)務,近年來,特別是在芯片技術發(fā)展到后摩爾時代,仍舊不斷顯示出巨大的商業(yè)機會。IP核顯然已成為芯片設計業(yè)的放大器。后摩爾時代的SoC設計需要越來越多的IP核。從商業(yè)機會來看,一個芯片制造企業(yè)所擁有的IP核數(shù)量的多少和質量的高低已成為其市場競爭力的核心;從國家戰(zhàn)略看,一個國家所擁有的IP核體現(xiàn)了其搶占集成電路戰(zhàn)略制高點的水平,其中IP核數(shù)量多、質量高則成為芯片產業(yè)的制高點。事實上IP核已成為集成電路產業(yè)在實施大眾創(chuàng)新時不可或缺的低成本利器。

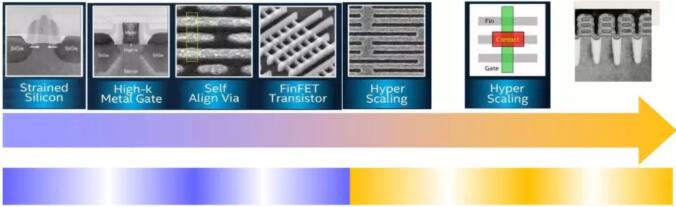

IP的技術發(fā)展與工藝技術發(fā)展密切相關。目前全球主流的先進工藝技術是10/7 nm成套工藝,未來3年內5 nm的成套工藝也將進入產業(yè)化階段。而芯片制造技術,從以三維晶體管FinFET結構為主線的技術路線,擴展到全方位的技術創(chuàng)新。其創(chuàng)新點主要有3方面,即晶體管結構、材料和工藝、以及芯片結構的創(chuàng)新。

隨著2D平面技術向3D技術的發(fā)展,芯片設計也發(fā)生了極大的變化。從而根本上改變芯片晶體管的設計:包括3D維度的FinFET芯片設計、圍柵(gateall-around,GAA)、量子隧穿效應(quantum tunnelingeffect)等。進入28 nm技術代以后,平面晶體管的比例縮小到了極限,3D晶體管逐漸形成主流。預計主流技術依然采用3D的FinFET架構和浸沒式193 nm(i193)波長的光刻技術。圍柵結構由于工藝復雜,成本必然上升,所以最早可能在5 nm節(jié)點應用。如圖3所示是全球集成電路產業(yè)主流的晶體管結構發(fā)展路線圖,其技術發(fā)展的主要目標是提高性能功耗比。同時由于物聯(lián)網(wǎng)的市場驅動,超低功耗的器件研究 ,如隧道場效應管(tunnel field-effect transistor,TFET)等,也將是集成電路的技術發(fā)展方向,與之伴隨的外延、沉積、刻蝕、CMP等設備及相關材料的研發(fā)都是需要跟進的。尤其是光刻技術,從浸沒式193 nm多重曝光到EUV光刻工藝的技術門檻還沒有完全跨過去。EUV的掩模版技術在批量生產時遇到一些瓶頸,例如掩模版的缺陷檢測,保護膜(pellicle)的耐用性等問題還未解決,大規(guī)模的產業(yè)化應用還有很艱難的路要走。可以預料,未來僅以特征尺寸縮小為標志的技術發(fā)展速度將會減緩,而功耗和性能技術進步將成為產業(yè)技術發(fā)展趨勢。

圖3.全球集成電路產業(yè)主流晶體管結構發(fā)展路線圖(黃如院士提供)

目前,國內還沒有類似國外有規(guī)模的專門設計IP硬核的公司,芯片設計公司的成功設計還不能被定性為IP。國內已經(jīng)有專門提供IP軟核的公司,可以以RTL形式提供給用戶。針對上述現(xiàn)狀與差異,我國的IP核發(fā)展主要有3個方向,即高端處理器的IP核、高速接口類的IP核以及與產品應用密切相關的應用類IP。其中高端處理器的IP核被國外完全壟斷(如ARM),國內產品基本處于空白狀態(tài)。由于高端處理器短期內沒有盈利的可能,目前國內沒有IP公司開展相關研發(fā),也看不到任何發(fā)展計劃。在嵌入式處理器的IP核方面,由于門檻不像CPU那么高,又有較高的盈利空間,目前有一些國內公司在開展研發(fā);接口類的IP( 如 SerDes、DDR和USB等),國內有幾家公司已經(jīng)打開了良好的研發(fā)和市場局面。至于應用類的IP基本上都是由芯片設計公司和芯片制造企業(yè)自行研發(fā)完成。同時,由于國內14 nm技術代即將完成工藝研發(fā),所以亟需建立相對完備的14 nm IP庫。

截止于2018年,我國現(xiàn)有的1698家芯片設計企業(yè)中,90%以上企業(yè)的營業(yè)額在1億元以下。這些設計企業(yè)的發(fā)展主要依賴于中國市場,而其技術積淀不足。這些企業(yè)無法關注到每一個技術環(huán)節(jié)的發(fā)展,其有限的技術研發(fā)資源只能聚焦于某些產品的開發(fā),不可能全面鋪開。尤其是在一些通用IP核的使用方面,需要企業(yè)有工藝支持和設計服務的基礎。

企業(yè)需要進一步重視IP的知識產權價值,尤其在當前國際競爭的熱點上,需要加強自身IP的保護,也要用好別人的IP,這樣才不會把自己放到不可控的知識產權風險中。

完全自主可控的芯片設計IP核技術仍然是制約我國集成電路設計發(fā)展的重要因素之一。我國的IP企業(yè)基本上屬于小而散模式。雖然10年來累積了一批IP核,但是由于缺乏技術支持服務和工藝基礎,使得IP核的利用率很低,已有的IP缺乏維護,逐漸失去競爭力。缺乏完善中立的測試體系,IP企業(yè)又不愿意投入研發(fā),使得國內芯片企業(yè)要從國外采購大量的IP核。究其原因在于IP研發(fā)資金投入大且研發(fā)周期長,例如,130 nm工藝IP開發(fā)近500萬美元,需要耗時約18個月;28 nm技術節(jié)點的IP研發(fā)需要近1000萬美元和約21個月的研發(fā)周期。這導致國內IP公司很難在市場支撐下開展自主IP研發(fā),從而對我國產業(yè)發(fā)展埋下了極大的隱患。

業(yè)界IP設計技術專家朱敏先生認為,集成電路產業(yè)的特點是投入大,回報周期長。集成電路芯片產業(yè)的現(xiàn)狀是一個芯片制造的代工廠(28 nm,月產4萬片)需要投資近50億美元,大多設計企業(yè)沒有這么大的資金投入,也沒有必要花費大量資源運行生產線,所以利用代工共享產能是[敏感詞]的選擇。然而,IP的研發(fā)和應用也有類似情況。開發(fā)新一代工藝節(jié)點(28 nm)上的IP需要投入近1000萬美元,以及至少6個月以上的研發(fā)周期,多數(shù)設計企業(yè)無法在每一代的產品設計中有那么大資源投入,所以IP也需要共享。IP核共享是支撐產業(yè)鏈整體發(fā)展的重要環(huán)節(jié)之一。

為此,需要有一個IP核共享的公共平臺。公共平臺依靠國內的芯片制造的工藝基礎,為設計公司提供設計服務。我國蓬勃發(fā)展的集成電路產業(yè)急需一個中立的IP公共平臺提供設計服務。充分利用國內優(yōu)質IP公司和研究所、高校的優(yōu)質資源,組織產學研聯(lián)合團隊開發(fā)IP核 ,通過公共平臺支持設計公司創(chuàng)新驅動。同時具備中立的IP核測試評估,IP核的工藝驗證和IP核相關的設計服務,包括公共IP平臺和電子設計自動化(electronic design automation ,EDA)工具平臺的支持。其結構類似于法國的Design Reuse IP公共平臺。

公共IP設計服務平臺扮演著連接設計企業(yè)與各芯片制造企業(yè)橋梁角色。我國的產業(yè)需要建設一個公共IP平臺,從工藝平臺建設和基礎的模型研究開始,扎扎實實地提升我國的IP核技術水平和應用規(guī)模。如圖4所示,公共IP平臺的架構是以工藝平臺為基礎,建立相應的模型,工藝設計(智囊)包(process design kit,PDK)及單元庫(library),真正發(fā)揮連接設計和制造的橋梁。

集成電路技術60年來基本遵循摩爾定律演進規(guī)律。隨著進入后摩爾時代,即兩年一代技術更換的節(jié)奏開始放緩,設計和制造企業(yè)開始更加重視產品的多樣化發(fā)展,而不再一味追求特征尺寸的縮小,使得IP技術發(fā)展也出現(xiàn)新的趨勢。IP技術發(fā)展趨勢可以認為有6個方面。

3.1 IP技術與工藝結合愈發(fā)緊密,同步變革

IP核是集成電路設計和制造環(huán)節(jié)的關鍵組成部分,其發(fā)展趨勢和集成電路整體演進趨勢基本相同,都是向著工藝制程和精度尺寸不斷縮小,產品集成度不斷提高,整體性能不斷提升的方向發(fā)展。在工藝和設計關聯(lián)度越來越高后,也衍生出了設計制造協(xié)同優(yōu)化技術(design technology Co-optimization,DTCO),通過彼此協(xié)作滿足新制程節(jié)點器件的要求。

3.2 IP研發(fā)遵循統(tǒng)一性、簡單化、局部化原則

在IP的研發(fā)過程中,要特別注意到可復用的單個的IP核必須經(jīng)過組裝后才能有產品設計的價值。在組裝過程中,統(tǒng)一的IP核規(guī)范化非常重要,包括必須按特定的命名定義接口信號,統(tǒng)一復位方式、事先約定編寫代碼的習慣和風格。同時需要服從簡單化原則,因為簡單的模塊比較容易被第三方識別和理解,一個復雜功能的模塊需要由一系列功能盡量簡單的模塊組成。最后,需要服從局部化原則,各個局部模塊相互正交獨立,模塊間的接口需要顯式標出。局部化設計可以將成本、功能、時序等重要指標和獨立模塊相結合。

3.3 新一代高速接口IP走熱,新產品涌現(xiàn)

當前,PCIe(PCI express)4.0(2017;5.0,2019)、USB 3.2(2017)、DDR/LPDDR 5(2017)、HBM 2(高帶寬存儲器high bandwidth memory,HBM;V2/V3,2016)、SATA rev3、HDMI 2.1、MIPI DSI/DPI、Bluetooth 5(2016)和Ethernet(400 Gbps,2018)等接口標準的新版本 IP 正在不斷涌現(xiàn)。2018 年已經(jīng)有芯片企業(yè)推出了業(yè)內[敏感詞]個通過7 nm FinFET硅驗證的56Gbps PAM4(四級脈沖放大調制)SerDes IP。國內IP企業(yè)USB3.1 IP已經(jīng)得到了歐洲的證書,成為世界僅有兩家得到該證書的IP公司之一。

人工智能(AI)技術的發(fā)展帶來了計算模型的變革,一方面使得各大IP供應商紛紛推出為AI定制或與AI結合的IP,如Synopsys公司于日前推出了高性能嵌入式視覺處理器IP——DesignWare EV系列;另一方面人工智能算法也被用在IP相關的EDA工具當中,如華大九天推出的Empyrean Mcfly就是用人工智能算法實現(xiàn)IP驗證加速。

3.5 IP的研發(fā)應用呈現(xiàn)平臺化發(fā)展態(tài)勢

以成套工藝技術為基礎,IC設計數(shù)據(jù)為核心,以IP為核心資產的設計平臺正在成為設計公司的核心競爭力。IP平臺的主要任務是研發(fā)設計公司急需的IP以及提供相應的設計技術服務,并將IP的設計驗證貫穿整個設計過程,如圖5所示。

圖5.IP驗證貫穿于整個設計流程

傳統(tǒng)的驗證平臺(testbench)適用于小型設計,是一種基于斷言驗證(assertion-based verification,ABV)方法。對于IP在超大規(guī)模SoC與數(shù)模混合信號設計中的驗證與集成,基于事務級建模(transaction-level modeling,TLM)的通用驗證方法(universal verification methodology,UVM)已經(jīng)開發(fā)應用多年,并且不斷趨于成熟。在UVM技術中,根據(jù)設計特點和應用場景,設計者可以選用不同的驗證語言,對IP設計進行建模并驗證,如圖6所示。例如,對于小型與基于器件的設計,采用SPICE語言為主的驗證;對于模擬IP設計,采用Verilog-A語言作驗證;對于數(shù)模混合信號IP設計,可以采用Verilog-AMS語言進行驗證;對于超大規(guī)模的數(shù)字電路中應用的IP設計,則需要建立TLM,采用UVM,應用SystemVerilog語言進行驗證。

3.6 開源IP將為IP供應商帶來新的機遇與挑戰(zhàn)

后摩爾時代的產品設計將更加多樣化,嵌入式處理器因其功能的多樣性和靈活性,預計將迎來更大的市場空間。嵌入式處理器一般都是以IP核授權的商業(yè)模式運作,而ARM的IP核高昂的授權費用會使初創(chuàng)芯片設計公司的創(chuàng)新成本大增。因此,在眾多中小公司需求的驅動下,近年來一些開源的免費IP核也開始初露頭角。

當前,最典型的案例就是由美國加州大學Berkeley校區(qū)推出的RISC-V,可以提供免費的基礎40多條指令集和其他模塊化的數(shù)十條擴展指令。開源采用寬松的伯克利軟件套件(berkeley software distribution,BSD)協(xié)議(protocol),企業(yè)可以在Linux衍生的BSD系統(tǒng)上免費開發(fā)使用。由于 RISC-V的開源指令集近年來快速興起,眾多企業(yè)加入到RISC-V芯片的設計和實現(xiàn)中,對應產生的開源IP將會對現(xiàn)有龍頭IP供應商帶來挑戰(zhàn)。當然,成熟的IP必須經(jīng)過充分的驗證以保證其可靠性和復用性,避免風險。開源 IP帶來新機會的同時也將面臨相應的考驗。

以下舉兩個例子說明高端工藝的設計與制造協(xié)同優(yōu)化和人工智能對IP檢查的應用是未來IP技術發(fā)展的必然途徑。

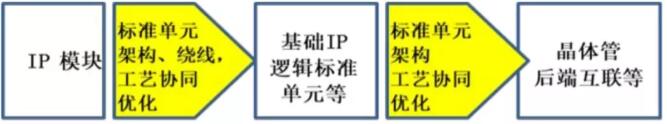

(1)設計和制造協(xié)同優(yōu)化(DTCO)。在基礎IP設計方法上,隨著技術發(fā)展,關鍵尺寸越來越小,工藝窗口越發(fā)窄小,工藝和設計相互獨立的模式導致工藝窗口無法滿足設計需求,必須將設計與制造的關系緊密結合。在設計過程中,需要根據(jù)芯片制造工藝的要求,服從一系列的設計規(guī)則。在工藝和設計規(guī)則的約束下,物理版圖的布局,布線對速度和信號的完整性,壓縮芯片的面積至關緊要。在28 nm技術節(jié)點以及更先進的技術節(jié)點上,一種新的設計和工藝協(xié)同優(yōu)化的概念和方法論DTCO開始被采用。從而可以從設計開始就給工藝留有足夠的窗口。設計工藝協(xié)同優(yōu)化的主要內容就是把基礎IP電路設計和工藝優(yōu)化放在一起全盤考慮,通過兩者的協(xié)同優(yōu)化,使集成電路特征尺寸的進一步微縮得以繼續(xù),并滿足市場對芯片功耗、性能、面積、成本(PPAC)的需要;也有觀點提出面積、功耗、性能、可靠性、可量產性(APPRY)為順序的設計與實現(xiàn)的方案;同時在可能的范圍內兼顧可制造性。采用DTCO的主要原因有以下兩點:1)僅僅靠工藝來實現(xiàn)進一步的微縮和芯片性能提升變得越來越有挑戰(zhàn)性;2)市場對芯片特征尺寸的微縮和性能的提升有著持續(xù)的訴求。例如,傳統(tǒng)浸沒式光刻工藝在單次曝光情況下已經(jīng)難以滿足要求。晶體管尺寸的進一步微縮開始越來越影響晶體管性能,譬如短溝道效應增強、應力下降、寄身電容增加,漲落增大等,后段互連金屬線在進一步微縮之后電阻電容急劇變化,這些因素必須與設計同時考慮進去。

具體的DTCO執(zhí)行如圖7所示。設計工藝協(xié)同優(yōu)化主要發(fā)生在工藝/器件開發(fā)和基礎IP設計之間。通常在工藝和基礎IP之間進行協(xié)同優(yōu)化,同時考慮到一定的繞線需求和策略,通過優(yōu)化疊代,定義工藝技術框架和標準單元設計構架,實現(xiàn)最優(yōu)化PPAC。一個完善的設計工藝協(xié)同優(yōu)化過程還會在達到PPAC目標的同時兼顧到可制造性,使具有競爭力的芯片產品在最快的時間內達到量產,推向市場。

(2)IP驗證采用人工智能技術。現(xiàn)代SoC設計中普遍會用到成百種IP單元模塊。這些IP的性能表現(xiàn)以及其IP庫交付數(shù)據(jù)質量是影響芯片性能以及整個設計周期的重要因素。設計公司需要對IP庫進行深入的性能分析比較、細致的交付項質量驗證和數(shù)據(jù)校驗后,才能確定一套適合設計要求的高質量IP庫以及相應的設計規(guī)則。業(yè)內已經(jīng)有IP交付物驗證解決方案,可以驗證IP數(shù)據(jù)的正確性和一致性。此外,近年來人工智能技術發(fā)展對IP技術有很大的促進作用。在IP的時序驗證過程中,機器學習的方法可以對IP進行檢查。例如基于CPU-GPU異構平臺架構異構計算平臺的電路仿真器 Empyrean ALPS-GT,性能較傳統(tǒng)的模擬電路仿真器加速1個數(shù)量級以上,可以大幅提升模擬IP的驗證效率。用人工智能技術做IP質量驗證,通過人工智能的方法學習以前的模擬IP情況,訓練出模型,讓AI為IP質量驗證服務。

以華大九天的Timing ARC驗證為例。TimingARC是時序計算中最關鍵、最基本的組成元素。如果IP單元的管腳之間在時序上存在因果關系,就稱之為 Timing ARC。應用傳統(tǒng)的檢查方法對IP的Timing ARC功能驗證有很大的局限性。這是因為基于規(guī)則檢查(rule- based)的方法無法支撐MissingARC的功能驗證。隨著IP規(guī)模變大,一個IP有數(shù)百甚至數(shù)千個輸入輸出,需要驗證的ARC達數(shù)百萬條。這顯然是傳統(tǒng)仿真測試方法在時間和資源上都無法滿足的,即便是國際[敏感詞]的大型IC設計企業(yè)花費大量人力資源(數(shù)十人)和時間(幾個月時間)也不能完美地完成IP的驗證。

而借助于人工智能的機器學習(machine learning,ML)技術,可以快速準確地幫助設計者對IP設計有效地檢查Missing Arc Validation等時序問題,其流程如圖8所示。在一個應用實例中,待分析IP包括PLL、TX、RX、PHY、LDO、HBM等,訓練集為16 nm工藝的30個IP,測試集為7 nm工藝設計的IP,訓練時間約為1h,對千萬量級Timing ARC的時序驗證在10 min內完成預測 。

圖8.利用AI-ML技術進行IP時序驗證流程示意圖(華大九天提供)

可以預測我國未來集成電路產業(yè)發(fā)展一定會相當快速。集成電路產業(yè)的頂層是設計IP核,因此我國必須對發(fā)展IP核有充分的當下認識和前瞻計劃。快速提升我國IP水平的基本策略就是:我們需要堅定不移地認識到要堅決走自主創(chuàng)新之路,優(yōu)先布局核心IP;依托精英團隊,重點突破關鍵IP;以常規(guī)IP為抓手,成熟工藝為基礎,大力建設公共IP平臺,支持產業(yè)健康發(fā)展。

(1)堅決走自主創(chuàng)新之路,優(yōu)先布局核心IP。核心IP的重要性一方面體現(xiàn)在其位于集成電路價值鏈[敏感詞]端,附加值高且擁有龐大的生態(tài)支持;另一方面體現(xiàn)在其產品往往用于涉及國家安全問題的關鍵領域。我國目前所處的國際局勢日益復雜,在關系到國家安全的芯片產品領域,必須制定長遠目標,堅持自主可控安全可靠的發(fā)展。經(jīng)過20多年的發(fā)展,我國已經(jīng)初步具備了核心IP自主創(chuàng)新的基礎,核心架構IP領域逐步深入,物聯(lián)網(wǎng)(IoT)、人工智能等市場創(chuàng)新IP產品層出不窮。一方面要繼續(xù)發(fā)揮科研院所和龍頭企業(yè)主力軍的作用,激發(fā)他們投身技術創(chuàng)新的積極性,加大自主創(chuàng)新力度;另一方面要進一步通過開發(fā)部分市場,把創(chuàng)新企業(yè)的高端技術應用到國家關鍵核心領域,充分發(fā)揮它們作為“生力軍”的作用。

(2)依托精英團隊,重點突破關鍵IP核研發(fā)和應用。關鍵IP是一個領域中產品競爭力的體現(xiàn),是某類產品或技術的瓶頸所在,也是從中低端向高端邁進的轉折點。當前[敏感詞]的高速串行接口SerDes、高速ADC/DAC等關鍵IP依然掌握在博通、ADI、TI等少數(shù)幾家龍頭企業(yè)手中。由于技術龐雜、種類繁多,類似Synopsys公司這樣的綜合IP供應商也不可能通過購買獲得大量關鍵IP。每一個關鍵IP通常都具有獨立的技術要點且技術性強大,其關鍵在于能否找到真正專業(yè)的、具有產業(yè)和產品背景的技術團隊去開發(fā)實施。因此,突破關鍵IP要依托專業(yè)的精英人才,要組織團隊進行專項攻關。這類團隊通過3~5年的時間就能在某一關鍵IP領域取得突破。

(3)以常規(guī)IP為抓手,成熟工藝為基礎,大力建設公共IP平臺,支持產業(yè)健康發(fā)展。經(jīng)過多年發(fā)展,我國的成熟工藝技術發(fā)展已有一定的基礎。常規(guī)IP已經(jīng)擁有很強的市場資源和技術儲備,尤其是一些有較長產品生命周期的工藝技術節(jié)點的IP。例如以55 nm和28 nm成套工藝為基礎的IP,可以依托制造現(xiàn)有的成熟工藝為基礎,針對量大面廣的產品(如MCP 等),依賴市場競爭進行發(fā)展。對于這類IP,政府不需要進行大量投入 ,只需營造良好的市場競爭環(huán)境和產業(yè)發(fā)展環(huán)境。因此 ,可以通過建設公共服務平臺支持常規(guī)IP發(fā)展,鼓勵有經(jīng)驗的人開發(fā)IP,打通IP交易應用渠道,通過市場競爭取得技術突破。

綜上所述,我國集成電路產業(yè)中的IP領域發(fā)展取得不小進步,同時也看到與世界主流的差距明顯。在趕超過程中,提出以下5項建議。

(1)組建企業(yè)聯(lián)盟形成合力。推動建立大產業(yè)專利分享聯(lián)盟,抱團取暖,共同攻克專利壁壘,抵御國際專利攻擊。通過自主創(chuàng)造、企業(yè)并購和海外專利收購等多種方式增加企業(yè)自身的知識產權積淀,同時輔以產業(yè)聯(lián)盟、利益聯(lián)盟等方式構建專利分享共同體。加大支持公共IP平臺建設力度。建議成立專業(yè)基金進行專業(yè)并購整合,增強綜合競爭力。

(2)加大知識產權保護。簡化IP侵權的直接和間接經(jīng)濟損失的認定辦法,從直接和間接經(jīng)濟損失補償轉向相對嚴厲的IP侵權的懲罰性條款,并在司法解釋和實踐方面逐步趨于嚴厲,打擊盜版侵權行為。充分利用我國在全球分工中的產業(yè)鏈及市場優(yōu)勢,針對海外訴訟采取一些行之有效的司法手段。成立相應的專利運營公司,參考國際商業(yè)化專利運營公司模式,共同抵御外國專利訴訟。

(3)構建差異化投資體系。建議考慮構建由國家產業(yè)基金、地方類基金和社會其他基金組成的多層次、全方位投資架構,面向不同規(guī)模的企業(yè)進行投資以及產業(yè)服務,以解決 IP 企業(yè)既需要投資,又擔心大筆投資會影響公司股權、管理模式的現(xiàn)狀。也可以成立各種類型的子基金去投資數(shù)額相對較小且有一定風險,但對產業(yè)有積極意義的IP企業(yè)。

(4)多渠道財稅和投融資支持。增加對IP核設計的資金政策支持,出臺相應稅收減免政策,建立專門面向IP核研發(fā)的基金項目,采取“平臺+項目”的運作模式,鼓勵引導IP核新產品開發(fā)。對IP核設計研發(fā)項目給予投融資支持、成長激勵和政策上的扶持,引導相關企業(yè)將研發(fā)力量集中突破國內急需的重點IP核領域。

(5)加大力度培養(yǎng)人才。重視相關專業(yè)人才的培養(yǎng),支持示范性微電子學院的建設,增加高校相關專業(yè)課程和科研項目,不拘一格地引進有經(jīng)驗的工程技術人員到高校講授相關技術課程,促進產學研用多方對接,以促成產業(yè)聯(lián)盟等形式實現(xiàn)協(xié)作創(chuàng)新,推動國內IP核產業(yè)的發(fā)展。鼓勵企業(yè)開展校企合作育人,形成學生培養(yǎng)到企業(yè)實習和就業(yè)的一體化培養(yǎng)鏈。引進具有豐富一線工作經(jīng)驗的高端人才組建團隊,培養(yǎng)青年人才。

本文從IP的屬性和技術特點,結合國內外的技術和產業(yè)現(xiàn)狀,討論了我國IP核技術發(fā)展趨勢。針對我們追趕中的發(fā)展道路,提出了相應的5項建議。供讀者參考。不妥之處希望大家批評指正。

免責聲明:本文轉載自“半導體行業(yè)觀察”,本文僅代表作者個人觀點,不代表薩科微及行業(yè)觀點,只為轉載與分享,支持保護知識產權,轉載請注明原出處及作者,如有侵權請聯(lián)系我們刪除。